Fターム[5F101BA18]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | FG型 (6,485) | FG形状構造 (858) | PN接合(FG内の) (5)

Fターム[5F101BA18]に分類される特許

1 - 5 / 5

半導体記憶装置及び半導体記憶素子

【課題】素子の面積を増大させることなく、かつ、コントロールゲート電圧を制御しなくとも、低電圧で書き込み量を大幅に増やすことが可能であり、また、安定して十分な書き込みを行うことが可能である不揮発性半導体装置を提供すること。

【解決手段】ドレインアバランシェホットエレクトロンにより書き込みを行う半導体記憶素子であって、第1導電型の半導体基板に形成された第2導電型の第1の半導体層と、前記第1の半導体層上に絶縁膜を介して設けられたフローティングゲートと、前記フローティングゲート下部の前記第1の半導体層の表面に形成されたチャネル領域と、前記チャネル領域に接触するように前記第1の半導体層上に設けられた第1導電型のソース領域及びドレイン領域とを有するMOSトランジスタであって、前記チャネル領域が2種類以上のキャリア濃度の分布をもつ半導体記憶素子とした。

(もっと読む)

半導体装置

【課題】不揮発性メモリセルの面積を増大することなく、かつ、製造プロセスを変更することなく、不揮発性メモリセルのデータ書き込み速度およびデータ消去速度の向上を図ることのできる技術を提供する。

【解決手段】データ書き込み・消去用の容量部CWE、データ読み出し用のMIS・FETQRおよび容量部Cを互いに異なる位置に分離した状態で配置する。容量部Cの容量電極FGC2を覆う絶縁層6上にキャップ電極CAPを設けることにより、容量部Cは、容量電極FGC2とp型のウエルHPW1との間の容量およびキャップ電極CAPと容量電極FGC2との間の容量を加算した容量を有する。また、データ書き込み・消去用の容量部CWEにおけるデータの書き換えはチャネル全面のFNトンネル電流により行う。

(もっと読む)

ポリシリコン浮遊ゲートにPN接合を形成した不揮発性メモリ・セル及びそのメモリ・セルを製造する方法

【課題】浮遊ゲート型の不揮発性メモリ・セル及びそのメモリ・セルを製造する方法を提供する。

【解決手段】ソース側(13B)上に軽くドーピングされたホウ素と、ドレイン側(13A)+チャネル領域(Ch)上に高度にドーピングされたヒ素又はリンとを有するP−N接合多結晶シリコン浮遊ゲート(13)により、ソース(11)とドレイン(12)とを有するメモリ・セル(10)のアレーを形成する。多結晶浮遊ゲート(13)におけるP−N接合(JU)を使用することにより、メモリ・セル(10)がデプリーションへ移行するのを阻止し、稠密な分布の消去しきい電圧VTを発生させることにより過消去特性を得ると共に、前記ゲート酸化物(30)を介する電子の移動が少ないので、デバイス寿命を改善する。

(もっと読む)

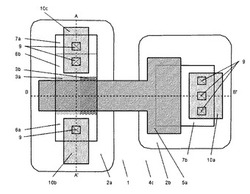

半導体装置

【課題】不揮発性メモリセルのデータ書き込みおよび消去用の素子において、チャネル全面のFNトンネル電流によりデータを書き換える。

【解決手段】フラッシュメモリの形成領域の半導体基板1Sのn型の埋込ウエルDNW内にp型のウエルHPW1〜HPW3を互いに分離した状態で設け、そのウエルHPW1〜HPW3にそれぞれ容量部C、データ書き込み・消去用の容量部CWEおよびデータ読み出し用のMIS・FETQRを配置した。データ書き込み・消去用の容量部CWEでは、チャネル全面のFNトンネル電流によりデータの書き換え(書き込みおよび消去)を行う。

(もっと読む)

半導体装置及びその製造方法

【課題】書き込みをしたセルにおいて、他のセルを書き込み中に誤消去が起こることがない半導体装置及びその製造方法を提供すること。

【解決手段】本発明の一形態の半導体装置は、半導体基板(1)と、前記半導体基板上に形成されたゲート絶縁膜(3)と、前記ゲート絶縁膜上に形成されたゲート電極(4)と、前記半導体基板に形成された拡散層(10)と、を備えた半導体装置において、前記拡散層付近の前記ゲート電極の所定部分に、前記ゲート電極の他の部分と導電型が異なる不純物領域または他の部分と導電型が同じであり、濃度がそれよりも低濃度である不純物領域を有する。

(もっと読む)

1 - 5 / 5

[ Back to top ]