Fターム[5F102FB05]の内容

接合型電界効果トランジスタ (42,929) | 特殊動作 (121) | トンネル電流制御素子 (5)

Fターム[5F102FB05]に分類される特許

1 - 5 / 5

環状構造をもつ縦型共鳴トンネル素子の製造方法及び縦型共鳴トンネル素子並びに磁気検出装置

【課題】 微小でしかも強磁場下でも高感度に磁気検出ができる縦型共鳴トンネル素子の製造方法を提供する。

【解決手段】 ソース電極12となる金属膜と導電層からなるドレイン電極13との間に変調ドープ構造を持つ柱状半導体11を有し、柱状半導体11のソース電極12とドレイン電極13との間に前記金属膜と略平行な多重障壁層14,15を備え、柱状半導体11の中心軸部分にソース電極12側から有底穴17が形成された縦型共鳴トンネル素子の製造方法において、有底穴17を形成するとき有底穴17の底部が多重障壁層14,15を貫通しない深さにすることにより生じる空乏層によって多重障壁層間の電子閉じ込め領域16が実効的にリング状になる深さにする。

(もっと読む)

双方向単一電子計数素子

【課題】2つの微小伝導領域に対する結合を最大に設計・調整可能とし、ポイント接合の特性を独立に調整可能とし、1つの端子から出力される電圧の測定のみで十分として外部測定系を簡略化し、微小伝導領域に占有する電子の数の差に比例した電圧を生じさせ、電子の数が2以上変化するような状況においても動作可能とし、高温での動作を可能にする。

【解決手段】2つの端子3と端子4の間に、トンネル障壁5と微小伝導領域1とトンネル障壁6と微小伝導領域2とトンネル障壁7とを直列に接続する。また、微小伝導領域1と強く静電的に結合したポイント接合8と、微小伝導領域2と強く静電的に結合したポイント接合9を設け、このポイント接合8とポイント接合9の片側の電極を共通にして出力端子12に接続し、このポイント接合8とポイント接合9の反対側の電極はそれぞれ電源供給端子10と電源供給端子11に接続する。

(もっと読む)

スピンFET及びスピンメモリ

【課題】スピンFET/スピンメモリの低消費電力と高信頼性を実現する。

【解決手段】本発明の例に関わるスピンFETは、磁化方向が固定される磁気固着層12と、磁化方向が変化する磁気フリー層13と、磁気固着層12と磁気フリー層13との間のチャネルと、チャネル上にゲート絶縁層18を介して配置されるゲート電極19と、磁気フリー層13上に配置され、電場により磁化方向が変化する磁性層15とを備える。

(もっと読む)

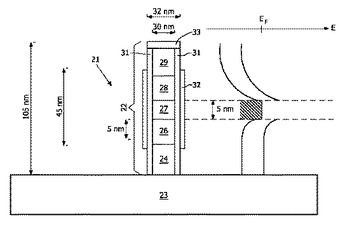

バリアを有するトンネルトランジスタ

本発明は、ソース(24)およびドレイン(29)、並びにこれらのソースとドレインの間に配置されたバリア領域(27)を備えたトランジスタ(21)を提案する。バリア領域は、半導体材料の真性または低濃度ドーピング領域(26,28)によってソースおよびドレインから分離されている。バリア領域と真性または低濃度ドーピング領域との界面にポテンシャルバリアが形成される。ゲート電極(32)はポテンシャルバリアの付近に設けられ、ゲート電極に適切な電圧を印加することによって、ポテンシャルバリアの実効的な高さおよび/または幅を調整することができる。  (もっと読む)

(もっと読む)

共鳴トンネル素子及びその製造方法並びに記憶素子

【課題】シリコン基板上に形成可能であり、かつ、負性微分抵抗を顕著に発現し得る共鳴トンネル素子及びその製造方法並びに記憶素子を実現する。

【解決手段】本発明の共鳴トンネル素子6は、エネルギー障壁を両端として、量子井戸とエネルギー障壁とが交互に連続するように形成されてなる多重障壁構造を有している。エネルギー障壁は熱酸化膜2であり、かつ量子井戸は金属ナノ粒子3である。負イオン注入によって、熱酸化膜2中に金属ナノ粒子3を形成する。

(もっと読む)

1 - 5 / 5

[ Back to top ]