Fターム[5F103DD09]の内容

半導体装置を構成する物質の物理的析出 (6,900) | 析出物質 (905) | 3−5族化合物 (251) | GaInSb (4)

Fターム[5F103DD09]に分類される特許

1 - 4 / 4

半導体装置の製造方法及び半導体装置

【課題】 ミスフィット転位の発生を抑制しつつ、量子ドットからの発光波長を長波長化することができる半導体装置の製造技術が望まれている。

【解決手段】 チャンバ内に単結晶基板を装填し、単結晶基板上に、分子線エピタキシにより、In及びAsを含む量子ドットを形成する。チャンバ内で、量子ドットに、少なくともAs2分子線を照射しながら第1アニールを行う。

(もっと読む)

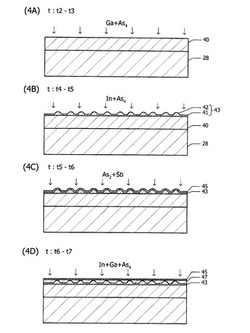

半導体量子ドット及び同形成方法

【課題】

巨大アイランドの形成による結晶品質の低下という問題を引き起こすことなく、ナノ構造の品質・形状を高品質に保つことを可能とする半導体量子ドット及び同形成方法を提供すること。

【解決手段】

本願に係る半導体量子ドット形成方法は、自己組織化機構により半導体量子ドットを形成する方法において、量子ドットDの結晶成長レート及び/もしくは埋め込み層L4の結晶成長速度として1ML/s(モノレイヤー・パー・セカンド)以上によって層形成させる。

(もっと読む)

オプトエレクトロニック半導体素子およびその製造方法

本発明は、分子線エピタキシーによって半導体ヘテロ構造を製造するための方法に関するものであり、以下のステップを有する。それらは、基板を第1の真空チャンバに導入するステップと、基板を第1の温度に加熱するステップと、第1のエピタキシャル層を生成するステップであって、当該層は、III族およびV族典型元素の2元、3元または4元化合物を含む第1の材料を含み、少なくとも1つの分子線から堆積されるステップと、前記基板を第2の温度に冷却するステップであって、III族およびV族典型元素の分子線を遮るステップと、基板を第3の温度に加熱するステップと、第2のエピタキシャル層を生成するステップであって、当該層は、III族およびV族典型元素の2元、3元または4元化合物を含む第2の材料を含み、少なくとも1つの分子線から堆積されるステップとである。さらに、本発明は、ここで述べた方法によって得ることができる半導体素子に関する。  (もっと読む)

(もっと読む)

半導体薄膜素子の製造方法

【課題】電子移動度の低下を最小限に抑えつつ、抵抗の温度依存性を低減させ、さらに薄膜製作の再現性や制御性に優れた、n型ドーパントとしてSnを含むInSb薄膜を用いた半導体薄膜素子の製造方法を提供する。

【解決手段】基板上に直接的にまたは有機物接着層もしくはバッファ層を介して間接的に積層されたInSbを含む化合物半導体薄膜層からなる動作層中もしくは該動作層に隣接したIII−V族化合物半導体層をMBE法により形成する際に、ドーパントとしてSnを、基板温度380℃〜400℃の範囲、SnのKセル温度500℃以上かつ1000℃以下の範囲でドーピングする。

(もっと読む)

1 - 4 / 4

[ Back to top ]