Fターム[5F110NN65]の内容

Fターム[5F110NN65]の下位に属するFターム

LOCOS (413)

Fターム[5F110NN65]に分類される特許

961 - 962 / 962

分離領域を有する半導体デバイスを形成するための方法

分離構造を有する半導体デバイス(10)を形成するための方法が漏れ電流を低減する。チャネル分離構造(32、30、34)がチャネル構造の中の漏れ電流を低減する。さらに、電流電極領域の下に電流電極誘電体分離構造(36)が形成され、電流電極(40)間の漏れを防ぐ。  (もっと読む)

(もっと読む)

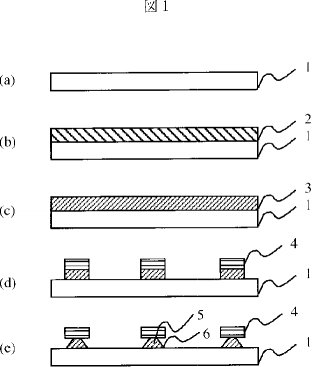

薄膜トランジスタ装置およびその製造方法

【課題】 電気特性の優れた多結晶TFTを提供する。

【解決手段】多結晶膜3を堆積させる工程、堆積した多結晶膜のうち所望の位置4のみを残すようにエッチングする工程、残された部分的な多結晶膜の中で所望の結晶方位の結晶粒5だけを、しかも所望の結晶面(ファセット)6を出した状態になるように異方性エッチングする工程、さらに、こうして得られた結晶核の上に膜を堆積し結晶化させる工程を用いる。

(もっと読む)

961 - 962 / 962

[ Back to top ]