Fターム[5F140AC07]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 動作、用途、素子構造 (4,642) | 常温以外での動作 (6)

Fターム[5F140AC07]に分類される特許

1 - 6 / 6

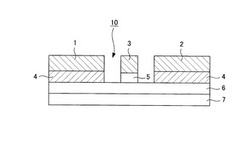

半導体結合超伝導三端子素子

【課題】超伝導電極層としてMgB2、接合部にInGaAsチャネル層を用い、第三電極を用いて超伝導電流を制御する半導体結合超伝導三端子素子において、超伝導電極層の成長時のMgのInGaAsチャネル層への拡散を抑制し、接合特性を改善した半導体結合超伝導三端子素子を提供することにある。

【解決手段】超伝導電流のチャネル層となるInGaAs層とソース電極となる第1のMgB2超伝導電極層及びドレイン電極となる第2のMgB2超伝導電極層とその二つの超伝導電極間のInGaAs層中に流れる超伝導電流を制御する第三電極とを有する半導体結合超伝導三端子素子において、MgB2超伝導電極層1,2とInGaAsチャネル層6との層間にAu層6が挿入された。

(もっと読む)

絶縁ゲート型電界効果トランジスタ回路

【課題】温度変化による動作特性の低下を抑制する電界効果トランジスタ回路を提案する。

【解決手段】本発明の例に係る絶縁ゲート型電界効果トランジスタ回路は、拡散層をそれぞれ備える第1のソース/ドレイン4S,4Dと、チャネル領域上に設けられる第1のゲート絶縁膜2と、前記第1のゲート絶縁膜2上に設けられる第1のゲート電極3とを有する第1の電界効果トランジスタTrと、半導体基板1とショットキー接合を形成する金属層をそれぞれ備える第2のソース/ドレイン14S,14Dと、チャネル領域上に設けられる第2のゲート絶縁膜12と、第2のゲート絶縁膜12上に設けられる第2のゲート電極13と、を具備し、第1のドレイン4Dと第2のドレイン14Dとが並列に接続される。

(もっと読む)

窒化物半導体素子および窒化物半導体素子の製造方法

【課題】チャネルが形成される部分における分極電荷の発生を抑えると共に、ブレークダウンの発生を抑制できる、窒化物半導体素子およびその製造方法を提供すること。

【解決手段】電界効果トランジスタは、n型GaN層3、p型GaN層4およびn型GaN層5が積層された窒化物半導体積層構造部2を備えている。窒化物半導体積層構造部2には、ドレイントレンチ6が形成されることにより、メサ積層部8が形成されている。メサ積層部8の壁面9は、n型GaN層5の頂面5aとの境界付近に位置する上側端部11と、n型GaN層3の上面3aとの境界付近に位置する下側端部12と、上側端部11と下側端部12との間に位置する中央部10とを有している。より具体的には、壁面9は、全体として傾斜角度の異なる複数の平面形状の傾斜部分17〜27を有している。そして、この壁面9には、ゲート絶縁膜15を挟んで、ゲート電極16が対向配置されている。

(もっと読む)

高温動作ダイヤモンドトランジスタ装置及びこれを用いた温度計、増幅器

【課題】高温下で動作するダイヤモンド半導体を使用して、高温下でも冷却装置を設けることなく動作させることができるダイヤモンドトランジスタ及びそれを使用した高温動作デバイスを提供する。

【解決手段】ダイヤモンド電界効果トランジスタ1はソース・ドレインとして、ボロンドープのダイヤモンド層3a、3bを使用し、チャネルとしてアンドープダイヤモンド層5を使用し、更に、ダイヤモンド層5上のゲート絶縁膜9上にゲート電極10が設けられている。このとき、ドレイン電流をId、絶対温度をT(K)、電界効果トランジスタ及びバイアス条件により決まる定数をa0、a1、ボルツマン定数をkB(1.38×10−23J/K)とすると、Id=a0・exp{−a1/(kB・T)}を満足する。

(もっと読む)

半導体装置及びその駆動方法

【課題】高い精度で電子の転送が可能でより高温で動作可能であり、かつより容易に製造ができる半導体装置を提供する。

【解決手段】半導体層101と、半導体層101の表面より形成されたp型領域102と、半導体層101の表面よりp型領域102と離間して形成されたn型領域103と、半導体層101の表面に形成されたゲート絶縁層104と、p型領域102とn型領域103との間のゲート絶縁層104の上に形成されたゲート105とを備える。加えて、p型領域102とn型領域103とに挟まれた半導体層101の表面より30nm以内の領域に導入された1個の不純物106を備えている。不純物106は、p型領域102とn型領域103とに挟まれたチャネル領域に導入されている。

(もっと読む)

チャネル材料として絶縁体−半導体相転移物質膜を利用した電界効果トランジスタ及びその製造方法

【課題】チャネル材料として絶縁体−半導体相転移物質膜を利用した電界効果トランジスタ及びその製造方法を提供する。

【解決手段】ゲート電界無印加時に、表面にホール電荷が流入しない第1状態と、負電界が印加されることにより、表面に多量のホール電荷が流入して導電性チャネルを形成する第2状態とを選択的に示す絶縁体−半導体相転移物質膜を備える電界効果トランジスタである。該絶縁体−半導体相転移物質膜上には、ゲート絶縁膜が配置され、絶縁体−半導体相転移物質膜に一定の大きさの負電界を印加させるためのゲート電極がゲート絶縁膜上に形成される。ソース電極及びドレイン電極は、絶縁体−半導体相転移物質膜が第2状態にある間、導電性チャネルを介してキャリアが移動するように、絶縁体−半導体相転移物質膜の両側から互いに対向するように配置される。  (もっと読む)

(もっと読む)

1 - 6 / 6

[ Back to top ]