Fターム[5F140BH49]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース、ドレイン領域及びSD近傍領域 (10,828) | 不純物濃度が規定されているもの (547)

Fターム[5F140BH49]に分類される特許

541 - 547 / 547

テーパ状単位セル金属酸化物半導体高電圧デバイス構造

電界効果電子デバイス(100,600)(例えばVDMOS等のFET)は、誘電体層(104,608)に隣接して配置されたフィールドプレート(105,607)を有しており、当該フィールドプレートは、半導体層(103,602)に隣接して配置されている。この場合、デバイスのドリフト領域は半導体層中にある。ドーピングレベルはドリフト領域に亘って略非線形的に変化し、デバイスは略一定の低減された表面電界を示す。電界効果デバイスの製造方法は、デバイスの半導体層のドリフト領域に非線形で不均一なドーピング密度を与えることを含んでいる。この場合、半導体層及び誘電体層の両方が一定でない厚さを有している。誘電体層は、low−k誘電材料によって形成され得る。  (もっと読む)

(もっと読む)

MIS型電界効果トランジスタ

下地SiGe層1上に歪みSi層2をエピタキシャル成長させ、ゲート絶縁膜3aとゲート電極4aを形成した後、ゲート電極4aをマスクにして、下地SiGe層1及び歪みSi層2に不純物をイオン注入し(図2(a))、活性化のための熱処理を行ってソース・ドレイン領域6を形成する(図2(b)、(c))。このとき、歪みSi層2の膜厚は、最終的なMISFETのソース・ドレイン領域6の不純物濃度が最大となる深さをTp(=Rp)としたとき、2Tp以下にする。 (もっと読む)

固相エピタキシャル再成長を用いて接合の漏損を低減させた半導体基板及び同半導体基板の生産方法

半導体デバイスの生産方法であって、(a)半導体基板を準備し、(b)適当な注入によって、第1の深さを有する第1のアモルファス層を前記半導体基板の最上層に作成し、(c)第1のドーピングプロファイルを伴う前記第1のアモルファス層を設けるために前記半導体基板の中に第1のドーパントを注入し、(d)前記第1のアモルファス層を部分的に再成長させ、前記第1の深さより小さい第2の深さを有する第2のアモルファス層を形成し、前記第1のドーパントを活性化する第1の固相エピタキシャル再成長作用を適用し、(e)前記第1のドーピングプロファイルより高いドーピング濃度を伴う第2のドーピングプロファイルを伴う前記第2のアモルファス層を設けるために前記半導体基板の中に第2のドーパントを注入し、(f)前記第2のアモルファス層を再成長させ、前記第2のドーパントを活性化するために、第2の固相エピタキシャル再成長作用を適用することを含む半導体デバイスの生産方法。  (もっと読む)

(もっと読む)

大量にドープされたエピタキシャルSiGeを選択的に堆積させる方法

一実施形態においては、基板上にシリコン膜又はシリコンゲルマニウム膜を堆積させる方法であって、プロセスチャンバ内に基板を配置するステップと、基板表面を約600℃〜900℃の範囲の温度に、プロセスチャンバ内の圧力を約13Pa(0.1トール)〜約27kPa(200トール)の範囲に維持しつつ、加熱するステップと、を含む前記が提供される。堆積ガスは、プロセスチャンバに供給され、SiH4、任意のゲルマニウム源ガス、エッチング剤、キャリヤガス、任意に少なくとも1つのドーパントガスを含んでいる。シリコン膜又はシリコンゲルマニウム膜は、基板上に選択的且つエピタキシャル的に成長する。一実施形態は、シリコン含有膜とキャリヤガスとして不活性ガスを堆積させる方法を含んでいる。方法は、また、選択的シリコンゲルマニウムエピタキシャル膜を用いる電子デバイスの製造を含んでいる。 (もっと読む)

半導体装置とこの種の半導体装置の製造方法

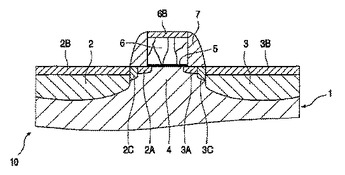

この発明は、基板と半導体本体(1)とを有する半導体装置(10)に関し、半導体本体(1)がソース(2)及びドレイン(3)を有する第一のFET(3)を備え、ソース(2)及びドレイン(3)は、金属シリサイドを含む接続領域(2B,3B)が設けられ、そして、ゲート(6)下部のチャネル領域(4)と境界を成し且つソース(2)及びドレイン(3)より厚みが薄く且つドーピング濃度が低いソース及びドレイン領域拡張部(2A,3A)に接続されている。ソース(2)及びドレイン(3)とソース及びドレイン領域拡張部(2A,3A)とは、第一の導電型で且つ厚み及びドーピング濃度がソース(2)及びドレイン(3)とソース及びドレイン領域拡張部(2A,3A)との間の中間領域(2C,3C)により互いに接続されている。このようにして、接続領域(2B,3B)と基板と間にリーク電流並びに短絡が起きるのが抑制され、一方で、ソース及びドレイン領域拡張部(2A,3A)を用いることの効果が維持される。好ましくは、中間領域(2C,3C)がゲート(6)直近のスペーサ(7)下部に位置し、好ましくは、これらは、なるべく傾けられたイオン注入により形成される。  (もっと読む)

(もっと読む)

絶縁トレンチゲート電極を有する横型電界効果トランジスタ

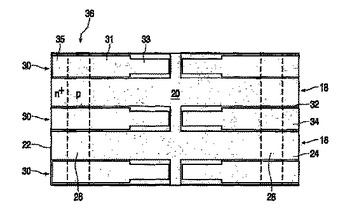

縦方向、横方向に交互に配置されたソース領域(22)、ソースボディ領域(26)、ドリフト領域(20)、ドレインボディ領域(28)、およびドレイン領域(24)をそれぞれ有するセル(18)を、減表面電界を達成するための構造とともに有する、電界効果トランジスタである。実施形態における構造は、ソースまたはドレイン領域(22、24)近傍にゲート領域(31)を定義する縦方向に離間された絶縁ゲートトレンチ(35)と、ドリフト領域(20)近傍に縦方向に延在する電位プレート領域(33)と、を含むことができる。代替的に、別個の電位プレート領域(33)または縦方向に延在する半絶縁フィールドプレート(50)をドリフト領域(20)近傍に設けてもよい。このトランジスタは、双方向切り替えに適している。  (もっと読む)

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】 サブミクロンCMOSトランジスタを、アナログCMOSトランジスタ、高耐圧MOSトランジスタ、バイポーラトランジスタ、ダイオードまたは拡散抵抗などと一緒に、それぞれの特性を劣化させることなく、同一基板上に混載すること。

【解決手段】 半導体基板1の一主面側にパンチスルーストッパー層を形成する際に、アナログCMOSトランジスタ、高耐圧MOSトランジスタ、バイポーラトランジスタ、ダイオードまたは拡散抵抗を形成する領域をマスクしてたとえばイオン注入をおこなう。それによって、サブミクロンCMOSトランジスタの形成領域にパンチスルーストッパー領域4を形成するとともに、アナログCMOSトランジスタ、高耐圧MOSトランジスタ、バイポーラトランジスタ、ダイオードまたは拡散抵抗の形成領域にパンチスルーストッパー領域が形成されるのを防ぐ。

(もっと読む)

541 - 547 / 547

[ Back to top ]