Fターム[5F140BK25]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース、ドレイン電極形成前の処理 (1,173) | コンタクトホールの形成 (1,071)

Fターム[5F140BK25]の下位に属するFターム

エッチング (548)

Fターム[5F140BK25]に分類される特許

521 - 523 / 523

半導体装置の製造方法およびその方法で得られる半導体装置

本発明は、シリコンの半導体本体がその表面に拡張領域を含む第1の導電型のソース領域及びドレイン領域と、前記ソース領域と前記ドレイン領域の間に前記第1の導電型とは反対の第2の導電型のチャネル領域と、前記チャネル領域上のゲート誘電体により前記半導体本体の表面から分離されているゲート領域と、を有し、第2の導電型で前記チャネル領域より高濃度のドーピング濃度であるポケット領域が前記拡張領域の下に形成され、前記ポケット領域は前記半導体本体に重イオンを注入することで形成され、注入後適温での第1のアニール処理およびより高い温度で早い立ち上がりの第2のアニール処理が行われる電界効果トランジスタを備える半導体装置の製造方法に関する。本発明によれば、その方法は、2つのアニール処理の間に、半導体本体の表面からポケット注入領域まで延びる半導体本体の表面領域にアモルファスシリコンを意図的に存在させることを特徴とする。これは、例えば適時に第1のアニール処理を中断すること、または第1と第2のアニール処理の間に不活性イオンを注入することで適切な領域をアモルファス化することにより得られる。このようにして、将来のCMOS装置の利点であるポケット領域7のきわめて急峻かつ狭いドーピングプロファイルが得られる。  (もっと読む)

(もっと読む)

空洞を有するシリコン基板上の高移動度MISFET半導体装置及びその製造方法

MISFETの高性能化を実現する高移動度歪みシリコン構造に、低欠陥かつ低コストで移動度を向上した半導体装置を提供する。MISFETの高性能化を実現する高移動度歪みシリコン構造として、空洞を有するシリコン基板上に、格子緩和シリコン・ゲルマニウム膜/濃度傾斜シリコン・ゲルマニウム膜を形成し、さらにその上に歪みシリコン膜を形成する。これにより、空洞近傍の格子の束縛が緩み、自由度が増すことにより、シリコン・ゲルマニウム膜の薄膜化が実現できるため、低欠陥かつ低コストで移動度を向上した半導体装置を提供できる。 (もっと読む)

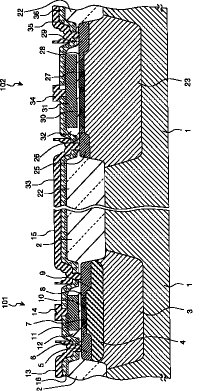

半導体集積回路装置およびその製造方法

【課題】 サブミクロンCMOSトランジスタを、アナログCMOSトランジスタ、高耐圧MOSトランジスタ、バイポーラトランジスタ、ダイオードまたは拡散抵抗などと一緒に、それぞれの特性を劣化させることなく、同一基板上に混載すること。

【解決手段】 半導体基板1の一主面側にパンチスルーストッパー層を形成する際に、アナログCMOSトランジスタ、高耐圧MOSトランジスタ、バイポーラトランジスタ、ダイオードまたは拡散抵抗を形成する領域をマスクしてたとえばイオン注入をおこなう。それによって、サブミクロンCMOSトランジスタの形成領域にパンチスルーストッパー領域4を形成するとともに、アナログCMOSトランジスタ、高耐圧MOSトランジスタ、バイポーラトランジスタ、ダイオードまたは拡散抵抗の形成領域にパンチスルーストッパー領域が形成されるのを防ぐ。

(もっと読む)

521 - 523 / 523

[ Back to top ]