Fターム[5F152BB02]の内容

再結晶化技術 (53,633) | 半導体素子等への用途 (2,062) | トランジスタ、ダイオード (1,748) | MOSFET、TFT (1,598)

Fターム[5F152BB02]の下位に属するFターム

下層ゲートTFT (331)

Fターム[5F152BB02]に分類される特許

1,261 - 1,267 / 1,267

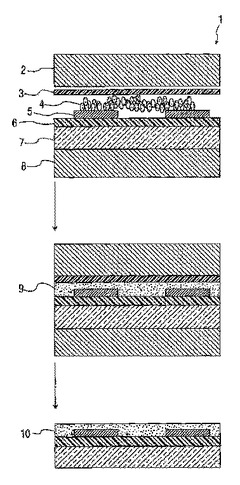

溶融技術により有機半導体デバイスを形成する方法

本発明は、有機半導体材料を有する半導体デバイスを形成する方法であって、溶融物を形成するために、有機半導体材料を有する組成物をこの組成物の融点若しくはガラス転移温度に又はそれよりも高い温度に加熱することと、溶融物を組成物の融点又はガラス転移温度よりも低い温度に冷却することとを有し、加熱する前又は加熱中にディウェッティングを抑制及び/又は防止することができる第1の物質若しくは物体が組成物に隣接するか、又は組成物がディウェッティングを抑制及び/又は防止することができる作用物質を更に有する方法を提供する。  (もっと読む)

(もっと読む)

半導体装置の製造方法および半導体検査装置

本発明に係る半導体装置の製造方法および半導体検査装置により、図2のフローに示すように、レーザ処理工程13で、SPC工程12処理後の基板の中から抜き取られたモニタ基板に、異なるレーザパワーで、異なる場所にレーザ処理を行い、基板全領域に多結晶シリコン膜を形成した後、最適パワー検査抽出工程14でモニタ基板上に形成された膜質の異なる多結晶シリコン膜を検査装置で測定し、レーザパワーの最適値が求められ、レーザ処理工程13で後続のSPC工程処理後の基板表面に、最適なレーザパワーに設定されたレーザが照射され、基板全領域で高品質な多結晶シリコン膜が製造される。  (もっと読む)

(もっと読む)

スタック状テンプレート層の局部的なアモルファス化及び再結晶化によって形成される、選択された半導体結晶配向を有するプレーナ型基板

【課題】 異なる配向の半導体が共通のBOX層上に配置された、プレーナ型ハイブリッド配向半導体基板構造体を形成するための、より簡単で優れた方法を提供すること。

【解決手段】 異なる結晶配向の半導体層を有するプレーナ型基板を製造するための、スタック状テンプレート層の局部的なアモルファス化及び再結晶化を用いる方法が提供される。本発明の方法を用いて構築されるハイブリッド配向半導体基板構造体、及び、デバイスの性能を高めるために異なる表面配向上に配置された少なくとも2つの半導体デバイスを含む種々のCMOS回路と一体化されたこうした構造体が提供される。

(もっと読む)

半導体基板を作製する方法

【課題】絶縁体上歪み半導体(SSOI)基板を作製する方法が提供される。

【解決手段】この方法で、歪み半導体は、あらかじめ形成された絶縁体上半導体基板の絶縁体層の上に直接配置された50nm未満の厚さを有する薄い半導体層である。本発明のSSOI基板を形成する際に、ウエハボンディングは使用されない。

(もっと読む)

レーザによりポリシリコン薄膜をアニールする光学系

被加工物の薄膜における配向又は結晶成長の変換を実行するためのガス放電レーザ結晶化装置であって、パルスドーズ制御に対してパルスを用いて光パワー及び高繰り返しレートでレーザ出力光パルスビームを生成するXeFレーザシステムを構成する主発信パワー増幅器MOPA又はパワー発信器パワー増幅器と、レーザ出力光パルスビームから伸長され

た細いパルス化作用ビームを発生させる光学系とを、有するガス放電レーザ結晶化装置について開示している。その装置において、レーザシステムはPOPAレーザシステムとして構成され、第1レーザPOユニットから第2レーザPAユニットに第1出力レーザ光パルスビームを方向付けるように動作されるリレー光学系と、第1レーザ出力光パルスビームの拡大として第2レーザ出力光パルスビームを発生するように、パルス又は−3nsec内で第1及び第2レーザユニットにおいてガス放電の発生のタイミングを合わせるタイミング及び制御モジュールとを更に有することが可能である。そのシステムは、発信器レーザユニットにおいて発散制御部を有することが可能である。発散性御部は不安定発振制御部を有することが可能である。そのシステムは、レーザと被加工物との中間にビームポインティング制御機構及びビーム位置制御機構を更に有することが可能である。ビームパラメータ計測法は、ビームポインティング制御機構に対するアクティブフィードバック制御部とビーム位置制御機構に対するアクティブフィードバック制御部とを与えることが可能である。  (もっと読む)

(もっと読む)

シリコン薄膜の焼鈍方法およびそれから調製される多結晶シリコン薄膜

後に絶縁層およびシリコン薄膜が形成される基板中のシリコン薄膜の焼鈍方法が開示される。本方法は、基板が処理中に変態しない温度範囲内でシリコン薄膜を加熱または予備加熱して、そこに内因性キャリヤを生成させることにより、抵抗をジュール加熱が可能な値に低下する工程;および予備加熱されたシリコン薄膜に電界を印加して、ジュール加熱をキャリヤの移動によって引き起こすことにより、結晶化を行い、結晶欠陥を排除し、結晶成長を確実にする工程を含む。本方法を用いると、予備加熱条件に従って、a−Si薄膜、a−Si/ポリ−Si薄膜またはポリ−Si薄膜にジュール加熱が選択的に引き起こされ、それによって良好な品質のポリ−Si薄膜が、非常に短時間に、基板を損傷することなく作製される。 (もっと読む)

歪みシリコン・オン・インシュレータ(SSOI)およびこれを形成する方法

【課題】 コストが低く歩留まりの高い、引っ張り歪みSOI層を形成するための方法および引っ張り歪みSOI層の構造を提供する。

【解決手段】 歪みSiベースの層を製造するための方法、この層に製造されるデバイス、ならびに、かかる層およびデバイスを含む電子システムを開示する。この方法は、基板上にSiGe層をエピタキシャル成長させるステップと、このSiGe層において様々なGe濃度を生成するステップを含む。SiGe層内のGe濃度は、Ge濃度が突然かつ著しく増大する固有のGeオーバーシュート・ゾーンを含む。SiGe層上に、Siベースの層をエピタキシャル堆積させ、これによって引っ張り歪みが与えられる。また、典型的にSiまたはSiGeである歪みSiベースの層を、異なるバルク基板または絶縁体に転写可能であることも開示される。

(もっと読む)

1,261 - 1,267 / 1,267

[ Back to top ]