Fターム[5H730BB08]の内容

DC−DCコンバータ (106,849) | 主変換部の型式 (20,669) | 充放電型(直並列切換) (1,313) | 蓄電素子としてFETを用いるもの (7)

Fターム[5H730BB08]に分類される特許

1 - 7 / 7

昇圧回路、昇圧装置及び半導体集積回路

【課題】電源ノイズ及び接地ノイズを低減することができる昇圧回路を提供すること。

【解決手段】本発明は、MOS容量C1、駆動回路10及びトランジスタ3を備える。MOS容量C1のゲートは出力端子VOUTと接続され、正の電荷が蓄積される。駆動回路10は、入力信号に応じて、MOS容量C1の一端に電源電圧VCCを出力し、又はMOS容量C1の他端にグランド電圧GNDを出力する。トランジスタ3は、出力端子VOUTと電源電圧VCCとの間に接続される。駆動回路10がMOS容量C1に電源電圧VCCを出力する場合は、トランジスタ3はOFFとなる。一方、駆動回路10がMOS容量C1にグランド電圧GNDを出力する場合は、トランジスタ3はONとなる。

(もっと読む)

DC/DCコンバータ及び液晶表示装置

【課題】チャージポンプの昇圧特性若しくは降圧特性を向上することができるDC/DCコンバータ及び液晶表示装置を提供する。

【解決手段】液晶表示装置のDC/DCコンバータにおいて、ガラス基板上に配設され、一方の主電極が出力端子に接続され、制御電極に制御信号が入力され、非単結晶半導体により構成された薄膜トランジスタ215cと、薄膜トランジスタ215cの他方の主電極に一方の電極が接続され、他方の電極に可変電圧が印加されるキャパシタ2132と、薄膜トランジスタ215cの他方の主電極及びキャパシタ2132の一方の電極と電源端子VDDとの間に電気的に直列に接続され、単結晶半導体により構成されたダイオード2131とを有するチャージポンプ214及び215を備える。

(もっと読む)

スイッチング動作速度を増加させるブースト回路を含む高電圧スイッチ回路およびこれを含むフラッシュメモリ装置

【課題】フラッシュメモリ装置において、スイッチング動作速度を向上させるとともに、出力される高電圧のノイズ成分を減少させる。

【解決手段】イネーブル信号に応答して出力ノードを設定された電圧にプリチャージするイネーブル制御回路と、出力ノードがプリチャージされるとき出力ノードで発生するスイッチ制御電圧に応答して入力ノードにフィードバック電圧を供給するフィードバック回路と、クロック信号に応答してフィードバック電圧をブーストしブースト電圧を出力ノードに出力することによりスイッチ制御電圧を増加させるブースト回路と、スイッチ制御電圧に応答してオンまたはオフされオンされるときに高電圧を受信して出力する高電圧スイッチとを備えて、高電圧スイッチ回路を構成する。ブースト回路は、クロスカップルドタイプの増幅回路を含む。

(もっと読む)

調整可能なトランジスタボディバイアス回路網

【課題】nチャネル金属酸化物半導体トランジスタと、ボディバイアス回路網と集積回路とを備える集積回路を提供すること。

【解決手段】集積回路であって、ボディ端子を有するnチャネル金属酸化物半導体トランジスタと、マイナスボディバイアス電圧を該ボディ端子へ印加する調整可能なチャージポンプベースのボディバイアス回路網とを備える、集積回路。上記集積回路は、プログラマブルロジックデバイス集積回路を備え、該集積回路は、構成データがロードされるプログラマブルエレメントをさらに備える。

(もっと読む)

内部電圧発生回路

【課題】チャージポンピング効率を最大化できる内部電圧発生回路を提供すること。

【解決手段】基準電圧VR1とポンピング電圧VPPとを受け取って、周期信号OSCを生成する周期信号生成部(110、120)と、周期信号OSCによってポンピング制御信号PS9、PS10、G11、G12と、電源電圧をポンピングしポンピング電圧を生成するブートストラップの両端ノード間をプリチャージさせるプリチャージ制御信号PB1を出力するポンプ制御ロジック部(130)と、ポンピング制御信号によってブートストラップの両端ノードを外部電圧でプリチャージし、ブートストラップの両端ノードの電圧とポンピング電圧とを電荷分配した後、プリチャージ制御信号の活性化によってブートストラップの両端ノードを接続してプリチャージさせて、昇圧された前記ポンピング電圧を生成するチャージポンピング部(140)とを備える。

(もっと読む)

半導体メモリ装置のチャージポンプ回路

【課題】差動入出力タイプを有するクロスカップルタイプチャージポンプ回路を提供する。

【解決手段】半導体メモリ装置のチャージポンプ回路において、チャージポンプのために互いに反対の位相で印加される第1及び第2入力信号を受信し、第1及び第2出力端がカスコード接続構造を有するトランジスタに接続されるクロスカップルロード部と、電流ミラー構造を有し、第1,2出力端の電圧にそれぞれ独立的に応答して、カスコード接続構造を有するトランジスタのうち対応するトランジスタのバイアスを独立的に設定するバイアス設定部を備える。

(もっと読む)

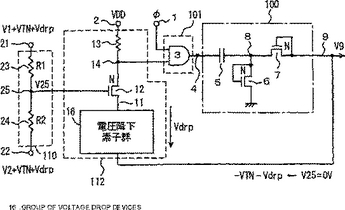

電圧検出回路およびこれを用いた内部電圧発生回路

所望の電圧の内部電圧を安定に生成する内部電圧発生回路及び電圧検出回路を提供する。電圧検出回路は、基準電圧をゲートに受ける絶縁ゲート型電界効果トランジスタと、この絶縁ゲート型電界効果トランジスタと直列に内部ノードの間に接続される電圧降下素子群を含む。基準電圧は、この絶縁ゲート型電界効果トランジスタのしきい値電圧と降下電圧を電圧成分として含む電源電圧を抵抗分割して生成される。基準電圧と内部電圧との差が所定値以上となると、この電圧降下素子群および絶縁ゲート型電界効果トランジスタに電流が流れ、検出ノードの電圧が低下し、内部電圧の低下が検出される。基準電圧はこのトランジスタのしきい値電圧及び電圧降下素子群の降下電圧を構成要素として含んでおり、これらのパラメータのばらつきを相殺して抵抗分割に所望の電圧を設定する。  (もっと読む)

(もっと読む)

1 - 7 / 7

[ Back to top ]