Fターム[5H740JB03]の内容

電力変換一般 (12,896) | 消弧制御 (632) | ターンオフ回路 (627) | ゲートに逆バイアスを印加するもの (42) | 主電流に比例させるもの (15)

Fターム[5H740JB03]の下位に属するFターム

コンデンサによるもの (11)

Fターム[5H740JB03]に分類される特許

1 - 4 / 4

半導体素子の駆動装置及び方法

【課題】半導体素子のスイッチング時において、スイッチング損失の増加を抑制しつつ、サージ電圧を低減すること。

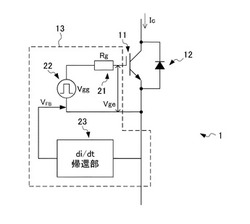

【解決手段】電子回路1は、IGBT11と、FWD12と、半導体素子駆動回路13と、を備えている。半導体素子駆動回路13は、IGBT11のゲート−エミッタ間の電圧Vgeを可変することによって、IGBT11のターンオン及びターンオフを制御する。半導体素子駆動回路13のdi/dt帰還部23は、電子回路1の主電流であるIGBT11のコレクタ電流Icの時間的変化、即ち時間微分値dIc/dtに基づき帰還電圧VFBを生成し、IGBT11のゲート−エミッタ間の電圧Vgeの一部として加算する。

(もっと読む)

出力遮断回路および電子機器

【課題】 簡単な回路構成で、素子の大きさを小さくすることができ、かつ負荷が短絡したとき、その素子の破壊を防止することができる出力遮断回路および電子機器を提供する。

【解決手段】 時刻t1に負荷が地絡し、出力電流Ioutが増大すると、電流検出用抵抗Rsでの電圧降下が増加し、トランジスタQ2がオンとなる。トランジスタQ2は、直流電源11から供給される電流をコレクタ電流Icとしてゲート抵抗Rgに流し、ゲート電圧VGを上昇させ、出力電流Ioutを制限電流値Ilimで制限する。ゲート抵抗Rgを流れる電流の一部がタイマ用コンデンサC1を充電し、トランジスタQ3のベース電圧が上昇すると、トランジスタQ3はオンになる。トランジスタQ3がオンになると、トランジスタQ2はフルオン状態となり、トランジスタQ1のゲートソース間の電圧がほぼ0Vとなり、トランジスタQ1はオフし、シャットダウン状態となる。

(もっと読む)

サイリスタ用ゲート駆動装置

【課題】サイリスタ素子がターンオフ時に故障しないようにする。

【解決手段】サイリスタ素子2の制御電極3のゲート電圧を正電位にする順バイアス電圧手段5と、負電位にする逆バイアス電圧手段6とを具備したサイリスタ用ゲート駆動装置において、サイリスタ素子の主電極に流れる陽極電流又は陰極電流の電流値を監視する電流監視手段10と、この電流監視手段で検出された電流値が入力され、この入力された電流のサイリスタ素子がターンオフ開始直前の電流値が、サイリスタ素子のオン電流最大定格値に対してどのくらいの割合であるかを演算する電流演算手段11と、この電流演算手段の出力値に対応して、サイリスタ素子の制御電極に印加するゲート電圧の逆バイアス定常値を制御する逆バイアス定常値制御手段12とを備えている。

(もっと読む)

スイッチング回路のためのドライバおよび駆動方法

駆動回路は、ハイおよびローサイドスイッチ(6,8)の状態を監視するための監視回路(32,34,36)を含む。駆動回路は、トランジスタ(6,8)をターンオンするための、調節可能な遅延を有する。一方のトランジスタに対応する電圧が所定電圧V1を通過するのが、他方のトランジスタに対応する電圧が別の所定点V2を通過するより前であることを、監視回路が検出すると、遅延は減少され、逆もまた同様である。  (もっと読む)

(もっと読む)

1 - 4 / 4

[ Back to top ]