Fターム[5H740JB04]の内容

電力変換一般 (12,896) | 消弧制御 (632) | ターンオフ回路 (627) | ゲートに逆バイアスを印加するもの (42) | 主電流に比例させるもの (15) | コンデンサによるもの (11)

Fターム[5H740JB04]に分類される特許

1 - 11 / 11

半導体素子のゲート駆動方法

【課題】ターンオフスイッチング時に発生するノイズとスイッチング損失のトレードオフ特性を改善する。

【解決手段】半導体素子をターンオフさせるとき、半導体素子のコレクタ・エミッタ間電圧がコレクタ・エミッタ間に印加された直流電圧に達するまでは、前記コレクタ・エミッタ間電圧の変化率を大きくし、半導体素子のコレクタ・エミッタ間電圧が直流電圧に達した後は、前記コレクタ・エミッタ間電圧の変化率を小さくする。

(もっと読む)

ゲート駆動回路

【課題】従来のゲート駆動回路で高速スイッチングさせる場合、複数の直流電源と、複数の制御用スイッチと、複雑な制御回路が必要で、装置が大型で、高価格となっていた。

【解決手段】制御用スイッチ直列回路の中点にスイッチング素子のゲート端子を、制御用スイッチ直列回路と並列に直流電源を、制御用スイッチ直列回路の正極端子と制御対象となるスイッチング素子のソース端子との間に小さい静電容量のコンデンサとダイオードとの並列回路と十分大きい静電容量を有するコンデンサとの直列回路を、スイッチング素子のソース端子と制御用スイッチ直列回路の負極端子との間に小さい静電容量のコンデンサとダイオードの並列回路を、各々接続する。

(もっと読む)

半導体スイッチング素子駆動用電源回路

【課題】従来の自給型ゲート駆動用電源回路では、RCDスナバ回路を充放電動作で使用するため、スナバ抵抗における充放電損失が大きくなり高周波動作では変換効率が低下し、装置が大型になる。さらに駆動用の電源として単一電源しか作れないため、IGBTのゲートに逆バイアスをかけることができずターンオフ損失が大きい。

【解決手段】上下アーム対の半導体スイッチング素子が交互にオンオフ動作することにより、上アーム側スイッチング素子駆動回路と、下アーム側スイッチング素子駆動回路との間に生じる電位差変動により充放電を繰り返すバイパスコンデンサを備え、バイパスコンデンサの充放電電流を上アーム側スイッチング素子駆動回路と下アーム側スイッチング素子駆動回路の各々の電源部に設けた整流回路で整流し、記整流回路の出力を各々のスイッチング素子駆動回路用電源とする。

(もっと読む)

電子回路

【課題】制御ICの有効利用を図る。

【解決手段】電源からの電圧を昇圧回路で昇圧して直列接続されたn個のLEDに供給する電子回路における昇圧回路のトランジスターをスイッチング制御するためのパルス信号を出力する制御IC30を使用し、直流電源22とLED24とを接続する電力ライン25にトランジスター(MOSFET)40を設け、制御IC30のDRV端子とトランジスター40のゲートとに積分回路50を接続し、積分回路50によりトランジスター40をリニア素子として動作させる。これにより、制御IC30を高電圧負荷駆動用のICとして用いることができると共に低電圧負荷駆動用のICとしても用いることができ、制御IC30に汎用性を持たせることができる。

(もっと読む)

電力変換器

【課題】損失を抑えつつ、負電圧を印加することによるスイッチング素子のターンオフを行う電力変換器を提供する。

【解決手段】ハイサイド駆動回路111a及びローサイド駆動回路131aは、第二電源140と、第一コンデンサ111c及び第一ダイオード111dからなるブートストラップ回路とにより常時正電圧が印加され、ハイサイド駆動回路111aは、第一電源111bにより常時負電圧が印加される。また、ハイサイド素子110がOFF、ローサイド素子130がONである間は、第一電源111bにより、ローサイド駆動回路131aへの負電圧の印加と、第二コンデンサ141への充電が行われる。そして、ハイサイド素子110がON、ローサイド素子130がOFFである間には第二コンデンサ141が放電され、ローサイド駆動回路131aに負電圧が印加される。

(もっと読む)

ゲート駆動回路、電力変換回路及びゲート駆動方法

【課題】本発明は、トランスへの入力電圧のデューティ比が略50%でなくても不具合が生じず、また小規模で小型な構成で実現できるゲート駆動回路、電力変換回路及びゲート駆動方法を提供することを課題とする。

【解決手段】トランス2の二次側に前記スイッチング素子と直列にコンデンサ13を設ける。またトランス2の二次側に並列にスイッチング素子4に印加される電圧がトランス2の二次側の電圧よりも低い値になるよう電圧を制限するツェナーダイオード16を設ける。そしてまたトランス2の二次側の電圧が0Vになる、若しくはスイッチング素子4が逆極性となったとき、PNPトランジスタ7によってコンデンサ13を短絡する。

(もっと読む)

スイッチ素子の制御手段

【課題】スイッチ素子のスイッチングを高速化できるスイッチ素子の制御手段について、小型化および高効率化すること。

【解決手段】スイッチ素子Qを制御するスイッチ素子制御回路1は、トランスTおよびツェナーダイオードDを備える。ツェナーダイオードDのアノードには、トランスTの2次巻線T2の一端が接続され、ツェナーダイオードDのカソードには、スイッチ素子Qのゲートが接続される。スイッチ素子Qは、ゲート−ソース間に入力容量Cissを内蔵する。

(もっと読む)

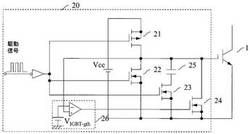

半導体素子のゲート駆動回路およびゲート駆動方法

【課題】ターンオフスイッチング時に発生するノイズとスイッチング損失のトレードオフ特性を改善する。

【解決手段】直流電源に第1MOSFET21と第2MOSFET22とを直列に接続し、半導体素子1のゲート端子を第1MOSFET21の負電位側端子と第2MOSFET22の正電位側端子に接続し、半導体素子1のエミッタ端子を第2MOSFET22の負電位側端子に接続するとともに、第2MOSFET22と並列にコンデンサ25と第3MOSFET23との直列回路を接続し、半導体素子1をターンオフさせるときは、第1MOSFET21をオフさせた状態で第2,第3MOSFET22,23をオンさせる。

(もっと読む)

半導体スイッチング素子駆動用電源回路

【課題】従来の自給型ゲート駆動用電源回路では、RCDスナバ回路を充放電動作で使用するため、スナバ抵抗における充放電損失が大きくなり高周波動作では変換効率が低下し、装置が大型になる。さらに駆動用の電源として単一電源しか作れないため、IGBTのゲートに逆バイアスをかけることができずターンオフ損失が大きい。

【解決手段】半導体スイッチング素子の両端電圧を直列コンデンサを介し、ハーフブリッジ形ダイオード整流器により整流して得られた直流中間点を持つ正負の直流電圧のうち、正側直流電圧を前記半導体スイッチング素子をオン駆動するための順バイアス側電源として供給し、負側直流電圧を前記半導体スイッチング素子をオフ駆動するための逆バイアス側電源として供給する。

(もっと読む)

電力変換装置

【課題】抵抗素子などの回路素子によって電流検出器の出力特性を調整する工程が不要な場合でも、電流検出ラインでの過電流を瞬時に検出し、応答の速い半導体スイッチ素子のオフ動作を行い、過電流に対して半導体スイッチ素子を保護する電力変換装置を得る。

【解決手段】電流検出器の電流検出感度およびオフセット電圧に応じた上限閾値電圧および下限閾値電圧のうちの少なくともいずれか一方を出力する制御信号生成手段と、検出電圧が上限閾値電圧より大きい場合または検出電圧が下限閾値電圧より小さい場合には、半導体スイッチ素子をオフ動作させるゲート遮断回路とを備える。

(もっと読む)

スイッチング回路

【課題】ノイズや電圧変動によって、2つの半導体スイッチング素子が同時に導通状態になる短絡の発生を確実に防止することができるスイッチング回路を提供する。

【解決手段】第1及び第2の駆動回路用電源回路4,5を、共通の直流電源Eを利用するように構成する。第1の駆動回路用電源回路を、第1及び第2のコンデンサC1及びC2と、コンデンサ充電回路と、順方向電圧印加回路と、逆方向電圧印加回路とから構成する。コンデンサ充電回路(Q3)は、第2の半導体スイッチング素子Q2が導通状態にある期間導通状態になって直流電源Eから供給される電荷で第1及び第2のコンデンサC1及びC2を充電する。第2のコンデンサC2の両端電圧を逆方向電圧として、第1のスイッチング素子用ゲート駆動回路Q1の第2の電源端子22と第1の半導体スイッチング素子Q1のエミッタとの間に印加する。

(もっと読む)

1 - 11 / 11

[ Back to top ]