Fターム[5J032AC00]の内容

論理回路 (717) | 目的、効果 (263)

Fターム[5J032AC00]の下位に属するFターム

入力しきい値に関するもの(ヒステリシスを含む) (2)

出力振幅に関するもの (4)

素子数の低減に関するもの (7)

消費電流、貫通電流の低減に関するもの (3)

高速化に関するもの (5)

信頼性に関するもの (237)

Fターム[5J032AC00]に分類される特許

1 - 5 / 5

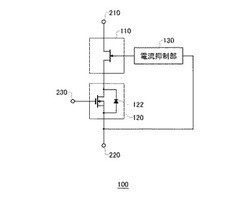

トランジスタ回路、双方向スイッチ回路、ダイオード回路及びトランジスタ回路の製造方法

【課題】トランジスタのゲートへの電流を防ぐ。

【解決手段】ノーマリーオン型の第1トランジスタと、ドレインが、第1トランジスタのソースと接続され、第1トランジスタとカスコード接続されたノーマリーオフ型の第2トランジスタと、第2トランジスタのソースと第1トランジスタのゲートとの間に設けられた、第2トランジスタのソースから第1トランジスタのゲートへと流れる電流を抑制する第1電流抑制部とを備えるトランジスタ回路を提供する。

(もっと読む)

半導体装置

【課題】スイング領域を変換せずに、CML領域でスイングする信号の電源電圧レベルをシフトすることができる回路を提供する。

【解決手段】第1の電源電圧VDD1を電源として用い、第1のレベルを基準としてスイングするCMLクロックCML_TRANS_Pを受信して、そのスイング基準レベルを第2のレベルに切り換えて降圧CMLクロックCML_TRANS_Lとして出力するスイングレベル切換部220と、第2の電源電圧VDD2を電源として用い、スイングレベル切換部220から伝達される降圧CMLクロックCML_TRANS_LをバッファリングするCMLクロック伝達バッファリング部240と、第1の電源電圧VDD1を電源として用い、ソースクロックCML_INをバッファリングして、CMLクロックCML_TRANS_Pを生成した後、スイングレベル切換部220に提供するCMLクロック生成バッファリング部200とを備える。

(もっと読む)

出力回路

【課題】過電圧低減保護対策ができ、かつバスリークを防止することができる出力回路を提供すること。

【解決手段】出力回路は、バスライン42と電源配線41との間に接続される過電圧保護部と、電源配線41と過電圧保護部との間に接続されるNchトランジスタN3と、バスライン42の電圧に応じてトランジスタN3のオン・オフを制御する制御回路23とを有する。過電圧保護部は、バスライン42とトランジスタN3との間に接続されるPchトランジスタP1と、トランジスタP1のバックゲートと電源配線41との間に接続されるNchトランジスタN2とを有する。

(もっと読む)

ラッチ回路

【課題】

本発明の課題は、論理回路が占める面積の増大が少なく、かつ、回路の反応速度の低下がないように、ソフトエラー耐性の強化を図ったラッチ回路を提供することにある。

【解決手段】

上記の課題を解決するため、反転回路から構成されており、2以上の入力端子を有するフィードバック回路と、フィードバック回路の入力端子に、クロックに同期して、入力信号又は入力信号と同相の信号を入力する入力回路と、を備え、フィードバック回路は、2以上の入力端子に、同時に入力信号又は前記入力信号と同相の信号が入力されたときのみ、入力端子に予め決められた増幅段数で正帰還がかかる構成となっていることを特徴とするラッチ回路を提供する。

(もっと読む)

半導体集積回路

【課題】半導体集積回路に搭載されるラッチ回路のソフトエラーレートを低減でき、救済情報等をラッチした場合にハードエラーと認識されるエラーの救済を可能とする。

【解決手段】不良アドレス等の情報を記憶した複数のフューズ素子10と、この複数のフューズ素子から並列に転送される複数の情報をラッチする複数の第1のラッチ回路11と、この複数の第1のラッチ回路から並列またはシリアルに転送される複数の情報をラッチする複数の第2のラッチ回路12と、これらの各ラッチ回路に入力する情報の転送を制御する転送制御回路13とを具備し、ラッチ回路にリフレッシュ機能を持たせている。

(もっと読む)

1 - 5 / 5

[ Back to top ]