Fターム[5J039BC09]の内容

Fターム[5J039BC09]に分類される特許

1 - 4 / 4

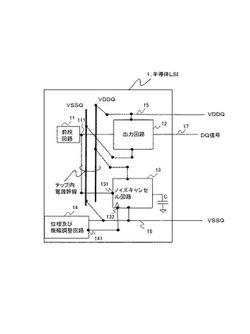

半導体装置

【課題】出力回路のSSN(Simultaneous Switching Noise)の振動ノイズの低減を可能とする半導体装置の提供。

【解決手段】第1及び第2の電源線と、前記第1の電源線VDDQと前記第2の電源線VSSQとの間に配置された出力回路12と、前記第1の電源線と前記第2の電源線との間に配置されたノイズキャンセル回路13とを備え、前記ノイズキャンセル回路13は、前記出力回路の前記出力ノードの論理レベルへの切り替え時に発生する所定の周期で指数関数的に減衰振動する電源ノイズに対して、前記電源に、前記振動から半周期分遅れ、前記振動と逆向きに減衰振動する電源ノイズを発生し、互いに打ち消し合わせる。

(もっと読む)

デジタル信号入力装置

【課題】動作が安定するとともに、後段に接続されるCMOSのLSIの安定な動作を実現するデジタル信号入力装置を提供する。

【解決手段】外部から入力された信号を増幅する増幅部と、前記増幅部で増幅された信号を波形整形する波形整形部と、オフセット電圧を保持するコンデンサと、前記波形整形部の出力をハイレベル状態に固定するように、前記コンデンサの充電と放電を制御して前記オフセット電圧を決定する制御部とを備える。

(もっと読む)

レベルシフト回路

【課題】 小規模な回路構成で入力信号と出力信号の電圧差が大きい場合であっても十分に動作し、かつ入力信号と出力信号との間で、デューティサイクル及び位相が同一であるレベルシフト回路を提供する。

【解決手段】 レベルシフト回路(3)は、所定の第1正側電源電圧VDD1と所定の負側電源電圧との間の振幅を有する2値の相反するレベルの一対の入力信号を、第1正側電源電圧VDD1よりも大きい所定の第2正側電源電圧VDD2と負側電源電圧との間の振幅を有する2値の相反するレベルの一対の信号にレベルシフトさせて出力する。レベルシフト回路(3)は、一対の入力信号を第2正側電源電圧VDD2と負側電源電圧との間の振幅を有する2値の信号にそれぞれレベルシフトさせて出力するレベルシフト回路部(4)と、レベルシフト回路部(4)からそれぞれ出力された2つの信号のレベル変化のタイミングを調整するタイミング調整回路部(5)とを備える。

(もっと読む)

混成信号集積回路

本発明は、混成信号集積回路、すなわちアナログ回路とデジタル回路の両方を備える集積回路に関する。本発明は特に、このような装置内のノイズ低減に関する。デジタル回路がアナログ回路と同じ集積回路装置内に含まれる場合は、デジタル回路がかなりの量のノイズの追加の発生源となり得る。その結果、アナログ信号にクロストーク、電気的干渉、および信号歪みが加えられる。本発明は、アナログ回路(26)とデジタル回路(29、30)を備える集積回路であって、デジタル回路がASM(30)を含む集積回路を提供する。ASMは、クロック信号を必要としない。その動作は適切な入力条件によってトリガされるが、SSMとは異なり、その入力に変化がないときはアイドルとなり、デジタル回路によって発生されるノイズ・レベルを低減する。  (もっと読む)

(もっと読む)

1 - 4 / 4

[ Back to top ]