Fターム[5J039KK30]の内容

Fターム[5J039KK30]に分類される特許

1 - 4 / 4

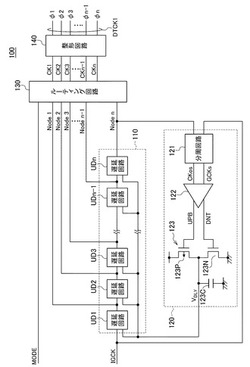

半導体装置及びこれを用いた情報処理システム

【課題】遅延回路の遅延量の最小値よりも短い相間隔を有する多相クロック信号を小さな回路規模で生成する。

【解決手段】縦列接続された遅延回路UD1〜UDnからなり、入力クロック信号IGCKをk周期遅延させるディレイラインと、遅延回路UD1〜UDnからそれぞれ出力される出力クロック信号Node1〜Nodenに基づいて互いに位相の異なる多相クロック信号DTCK1を生成するルーティング回路130とを備える。nとkの最大公約数をGCM、入力クロック信号IGCKの1サイクルをGCK、多相クロック信号DTCK1の相間隔をUIとした場合、相間隔UIの長さは、UI=GCK×GCM/nで与えられる。これにより、1個の遅延回路の遅延量の最小値よりも短い相間隔を有する多相クロック信号を小さな回路規模で生成することが可能となる。

(もっと読む)

ビット配列入れ替え半導体回路

【課題】基板上で接続されたマイコンとROM、RAMのデータのやりとり及びROM、RAMの内容を解析しづらくする。

【解決手段】

基板上で接続されたマイコンとROM、RAMを接続するデータバスに、スイッチング素子1を配置したビット配列入替回路を設け、アドレスバスの一部と、RAMまたは電気的に書き換え可能なROMとして実現されるメモリ3の内容を用いて、組み合わせ回路であるビット配列入替スイッチ駆動回路2により各スイッチング素子1のオンオフを決定することにより、データバスのビット配列の入替を行う。

(もっと読む)

EMIノイズを低減した同期回路の設計方法

【課題】 どの場所にどれだけスキューを付けられるかを検証して、消費電流が流れるタイミングを時間軸上で分散させることで、EMIのいずのピークを低減することができる同期回路の設計方法を提供すること。

【解決手段】 本発明に係る同期回路の設計方法は、ネットリストを含む所与の条件を入力して、自動配置配線ツールを用いて同期回路の一次配置配線を実施する第1工程と、配置配線された同期回路のクロックツリーに従って、クロックソースから各末端経路までのクロックの到達時間差であるスキューを解析する第2工程と、解析されたスキューがセットアップ/ホールドタイムに対してマージンを有する複数のモジュールI,II,III,IVに分割する第3工程と、分割された複数のモジュールI,II,III,IVの少なくとも一つにクロックスキュー設定回路10を追加挿入する第4工程と、クロックスキュー設定回路10を追加して、二次配置配線を実施する第5工程と、を有する。

(もっと読む)

シフトレジスタ及びその駆動方法

本発明は、インバータの入力部をインバータの閾値電位にし、インバータの入力部に容量手段を介してCK信号を入力することで、CK信号は増幅され、その増幅されたCK信号をシフトレジスタに用いる。つまり、インバータの閾値電位を取得することで、トランジスタの特性ばらつきに殆ど影響しないシフトレジスタを提供することができる。  (もっと読む)

(もっと読む)

1 - 4 / 4

[ Back to top ]