Fターム[5J049CA07]の内容

Fターム[5J049CA07]に分類される特許

1 - 13 / 13

疑似ランダムビット列発生器

【課題】高速動作可能な疑似ランダムビット列発生器を提供する。

【解決手段】疑似ランダムビット列発生器は、ハーフレート・クロック信号の所定のタイミングで入力信号を識別再生する、縦続接続された(N−1)/2個(Nは奇数)のDFF1−3,・・・,1−Nと、ハーフレート・クロック信号によって決定される動作タイミングがDFF1−3,・・・,1−Nの動作タイミングと180度位相が異なるタイミングで入力信号を識別再生する、縦続接続された(N−1)/2個のDFF1−2,・・・,1−N−1と、排他的論理和回路2と、ハーフレート・クロック信号の2倍の周波数のフルレート・クロック信号により排他的論理和回路2の出力信号を識別再生するDFF1−1とを備える。

(もっと読む)

論理回路、受信装置、及び論理演算方法

【課題】線形帰還シフトレジスタにおいて所望の構成を設定可能でありながらシフト演算の複数回分を並列且つ高速に計算可能な論理回路を提供する。

【解決手段】論理回路は、第1のデータを0乃至n−1ビットシフトし且つ空いたビットに0を挿入して得られる並列n個のデータの各々と第2のデータとの間でビット毎のANDを計算し、その結果の並列n個のデータの各々について全てのビットのXORを計算することにより、n個の1ビットデータを並列に生成するXOR処理部と、第1のデータをmビットシフトした状態での帰還データを生成するために、第1のデータを0乃至m−1ビットシフトしたそれぞれの状態での過去のm個の帰還データと第2のデータの対応ビットとの間でのビット毎のANDを計算し、その結果の全てのビットと第1のデータのmビットシフト状態での1ビットデータとのXORを計算する値生成処理部とを含む。

(もっと読む)

セキュリティチップ、セキュリティカード及び暗号化処理方法

【課題】発明の課題を簡潔に記載

【解決手段】スピン注入磁化反転現象を用いた第1の素子が少なくとも1個以上形成されてなり乱数を発生する乱数発生部と、スピン注入磁化反転現象を用いた前記第1の素子と同一積層構造の第2の素子がアレイ状に形成されるとともに前記メモリ部と同一チップ上に配置され、前記乱数発生部で書込み確率が1/2となるライト電圧に関する情報が保存されているメモリ部と、前記乱数発生部に対し前記書込み確率が1/2となるライト電圧で書き込みを行う過程を経て前記乱数発生部で生成された乱数を利用して任意のデータを暗号化する暗号化・復号回路部と、を備える。

(もっと読む)

乱数発生器および擬似乱数発生器

【課題】簡単な構成で高品質の乱数を発生する乱数発生器および擬似乱数発生器を実現する。

【解決手段】 回路3と回路4との間の信号を送受信する複数のバス線2Aから構成されたバス2と、信号の受信条件を動的に調整するキャリブレーション部5と、キャリブレーション部5の調整情報にもとづいて乱数を発生する乱数発生部10と、を有する。

(もっと読む)

乱数生成装置及び方法

【課題】 非線形関数を用いて、生成速度、周期長、統計的乱数性などが優れた乱数生成装置を提供すること。

【解決手段】

本発明に係る乱数生成装置は、非線形関数xt+1=4xt(1−xt)に従い、N(Nは2以上の整数)ビットの2進数列(初期値)を[((N−1)/m)]+1桁のm(mは1以上の整数、[ ]は小数点以下を切り捨て)ビットの整数に分割して、計算精度N、内部状態2Nビットを有する「カオス計算器」による整数の分割計算により、2Nビットの2進数列d(d0...d2N−1)を生成する手段と、dの上位Nビットd0...dN−1を再び「カオス計算器」の入力とし、dの特定のビット間にdiとd=i+N(i=0,1...N−1)と排他的論理和演算で得られたNビットの結果r(ri=di▲+▼di+N)を乱数として出力する手段とを備えたことを特徴とする。

(もっと読む)

乱数生成装置

【課題】良質な乱数を高速に発生させることができる高性能の乱数生成装置を提供することを可能にする。

【解決手段】振幅26mV以上のパルス波形電圧を発生するパルス電圧発生器70と、半導体基板上に離間して形成されたソースおよびドレイン領域と、ソース領域とドレイン領域との間のチャネル領域となる半導体基板上に形成されたトンネル絶縁膜と、トンネル絶縁膜上に形成されパルス電圧発生器からのパルス電圧が印加されるゲート電極とを有し、ソース領域とドレイン領域間に流れる電流にランダムノイズが含まれるランダムノイズ生成素子10aと、ランダムノイズ生成素子から発生されるランダムノイズの大きさに基づいて乱数信号を生成する乱数生成部30と、を備える。

(もっと読む)

ノイズ生成装置及びノイズ生成方法

【課題】ハードウェアによるノイズ発生処理を容易にし且つ処理部へのノイズデータの供

給速度を向上するのに好適なノイズ生成装置、ノイズ生成システム及びノイズ生成方法を

提供する。

【解決手段】ノイズ生成システム2を、ノイズ発生源10と、ノイズデータ生成装置20

とを含んだ構成とし、ノイズ発生源10は、比較的再現性の周期が長い乱数を発生する第

1の擬似乱数発生方法を用いて作成された第1のノイズデータを出力し、ノイズデータ生

成装置20は、ノイズデータ発生源10から、画素数Nの画像データの画素毎に、各画素

の各色に対応したn個の画素データに対して、1つの第1のノイズデータを取得する。更

に、前記取得した1つの第1のノイズデータに基づき、前記第1の擬似乱数発生方法より

も単純なアルゴリズムの第2の擬似乱数発生方法を用いて、n個以上の第2のノイズデー

タを生成し、当該生成した第2のノイズデータを画像処理部4に出力する。

(もっと読む)

雑音信号発生装置

【課題】広帯域で周波数密度が一定の雑音信号を短い処理時間で発生させる。

【解決手段】所望の雑音信号のスペクトラムをその上限周波数FMAXの1/Mとなる境界周波数Faで低域側と高域側に分け、各帯域について所望周波数分解能ΔFのM倍の値で上限周波数FMAXを除して得られる値をポイント数Nとするスペクトラムデータを生成して逆フーリエ変換を行い、得られた低域側の時間波形データDa(k)に対し、倍率Mの補間処理と境界周波数Faの低域通過フィルタ処理して所望周波数分解能に対応した時間波形データDa(k)″を生成し、得られた高域側の時間波形データDb(k)に対し、M通りの異なる遅延時間を与えて所望周波数分解能に等しい周波数差のあるキャリア周波数で境界周波数以上の高域帯へ周波数変換して複数Mの時間波形データDb1(k)〜DbM(k)に変換し、低域側の時間波形データと合成して所望の雑音信号を得ている。

(もっと読む)

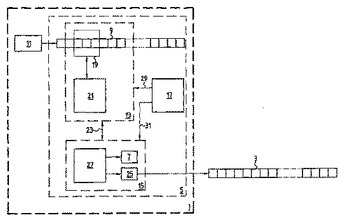

擬似乱数発生回路及び電子装置

【課題】高い周波数のクロック信号を用いることなくパラレル化した擬似乱数データを発生させることができる擬似乱数発生回路及び電子装置を得る。

【解決手段】本発明に係る擬似乱数発生回路は、1から順に番号を付けたM(15以上の自然数)個のシフトレジスタと、各シフトレジスタを接続する接続回路とを備え、各シフトレジスタは入力した信号を同一のクロック信号に合わせてシフトし、降番順のn(M以下の自然数)個のシフトレジスタの出力が、パラレル化した擬似乱数データとして出力され、接続回路は、m(M以下の自然数)番目のシフトレジスタに対して、関数F(m−n)の値を計算して入力し、関数F(x)は、0<xの場合はx番目のシフトレジスタの出力であり、x≦0の場合はF(x+14)とF(x+15)の排他的論理和で表される。

(もっと読む)

乱数生成回路及び半導体集積回路

【課題】 小型化を実現しつつ、高速化を実現することができる乱数生成回路及び半導体集積回路を提供する。

【解決手段】 乱数生成回路1において、ノイズ信号を発生するノイズ発生源2と、ノイズ信号の周波数帯域の一部を抽出するフィルタ3と、ノイズ信号の周波数帯域の一部と参照信号との間の信号差を増幅した乱数信号を生成するコンパレータ4とを備える。半導体集積回路は基板上に乱数生成回路1を搭載する。

(もっと読む)

疑似ランダムデータシーケンスの生成

疑似ランダムデータシーケンス(3)を生成する方法であって、前記疑似ランダムデータシーケンス(3)は、Nビットの初期データシーケンス(9)における検索パターン(7)に対する検索をするための手順によって生成されることを特徴とし、前記検索手順は、一組の検索パターンの1つであるrビットの特定の検索パターン(7)を前記初期データシーケンス(9)において検出する段階(E1)と、先行する段階(E1)の進行に依存する動作によってkビットの出力パターン(25)を判断する段階(E2)と、一連の出力パターン(25)から疑似ランダムデータシーケンス(3)を連続して形成するために先行する段階(E1、E2)を反復する段階とを具備する。  (もっと読む)

(もっと読む)

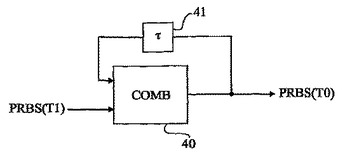

高速ランダムビットストリームの生成

第1の低クロック周波数で生成される擬似ランダム入力ビットストリーム(PRBS(T1 ))を、出力ビットストリームをサンプリングし、サンプリングされたストリームを所定値(t)分遅延させ、遅延させたストリームを入力ビットストリームと結合することにより第2の高クロック周波数での同一の出力ビットストリーム(PRBS(T0 ))に加速するための方法及び回路。  (もっと読む)

(もっと読む)

乱数発生素子

【課題】 回路規模が小さく偏りが少ない乱数発生素子を提供することを目的とする。乱数を発生させる速度が極めて速い乱数発生素子を提供する。

【解決手段】 並列に配置された一対の第1の電流路1及び第2の電流路2と、第1の電流路1及び第2の電流路2の近傍に配置され、相互に電荷が移動可能な一対の第1の微粒子3及び第2の微粒子4とを具備する乱数発生素子。

(もっと読む)

1 - 13 / 13

[ Back to top ]