Fターム[5J055DX24]の内容

電子的スイッチ (55,123) | 出力部 (8,827) | 主スイッチを構成する素子 (3,300) | 電界効果トランジスタ、FET (2,442) | 接合型FET (6)

Fターム[5J055DX24]に分類される特許

1 - 6 / 6

トランジスタの制御回路、トランジスタの制御システム、およびトランジスタの制御方法

【課題】ゲートとフィールドプレートとを有するトランジスタのスイッチング速度を速くする。

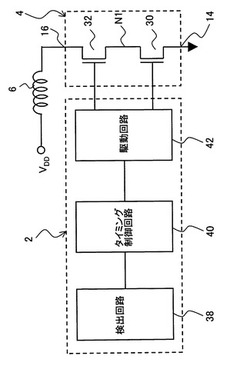

【解決手段】ゲートとフィールドプレートとを有するトランジスタ4を制御する制御回路2であって、トランジスタを駆動するタイミングを検出する検出回路38と、駆動するタイミングに応答してゲートを駆動する第1の駆動タイミングとフィールドプレートを駆動する第2の駆動タイミングとを制御するタイミング制御回路40と、第1の駆動タイミングに応答してゲートを駆動し第2の駆動タイミングに応答してフィールドプレートを駆動する駆動回路42とを有する。

(もっと読む)

エンハンスメントモード型およびデプレションモード型のワイドバンドギャップ半導体JFETのためのゲートドライバ

接合形電界効果トランジスタ(JFET)を駆動するための、DC接続2段ゲートドライバが提供される。JFETは、SiC JFETのようなワイドバンドギャップ接合形電界効果トランジスタ(JFET)であり得る。ドライバは、第1ターンオン回路、第2ターンオン回路及びプルダウン回路を含む。ドライバは、入力パルス幅変調(PWM)制御信号を受け入れて、JFETのゲートを駆動させるための出力ドライバ信号を発生させるように配置される。 (もっと読む)

ワイドバンドギャップ半導体パワーJFETのための高温ゲートドライバ及びそれを含む集積回路

高い周囲温度環境において作動することが可能なワイドバンドギャップ(例えば、>2eV)半導体接合形電界効果トランジスタ(JFET)のためのゲートドライバについて記載される。ワイドバンドギャップ(WBG)半導体デバイスは、炭化ケイ素(SiC)及び窒化ガリウム(GaN)を含む。ドライバは、入力、出力、第1供給電圧を受け取るための第1基準線、第2供給電圧を受け取るための第2基準線、グランド端子、6つの接合形電界効果トランジスタ(JFET)を有する非反転ゲートドライバであり得、第1JFETおよび第2JFETは、第1反転バッファを形成し、第3JFETおよび第4JFETは、第2反転バッファを形成し、及び第5JFET及び第6JFETは、高温パワーSiC JFETを駆動させるために使用され得るトーテムポールを形成する。反転ゲートドライバも記載される。 (もっと読む)

カスコード回路を有するスイッチング装置

第1の端子(1)と第2の端子(2)との間の電流を切り替えるためのスイッチング装置は、第1の半導体スイッチ(M)と第2の半導体スイッチ(J)との直列接続を有するカスコード回路を含む。上記2つの半導体スイッチ(M、J)は共通点(13)により互いに接続される。第1の半導体スイッチ(M)は第1の制御入力部と第1の端子(1)との間の電圧に従って第1の制御入力部により制御される。第2の半導体スイッチ(J)は、第2の制御入力部(4)と共通点(13)との間の電圧に従って第2の制御入力部(4)により制御される。最後に、特定可能な容量(C)を有する制御回路が第2の端子(2)と制御入力部の少なくとも1つとの間に接続される。  (もっと読む)

(もっと読む)

スイッチ回路

【課題】高周波用スイッチ回路としての歪み特性が悪くなってしまうという問題があった。

【解決手段】本発明のスイッチ回路は、入出力端子間に直列に接続されたトランジスタと、トランジスタの導通状態を制御する信号が入力される制御端子と、トランジスタの制御電極と制御端子間に接続された第1の抵抗と、制御端子とトランジスタの制御電極間に第1の抵抗と並列に接続された、ダイオードと第2の抵抗の直列回路を備えたことを特徴とする。

(もっと読む)

スイッチおよびスイッチ制御方法

【課題】

互いに逆の論理状態を必要とするシリーズFETおよびシャントFETを含み、1つの制御信号で駆動可能であるスイッチおよびその制御方法を提供する。

【解決手段】

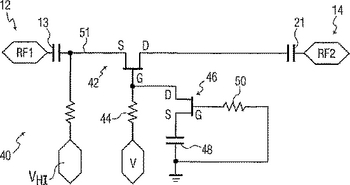

少なくとも1つのシリーズFET42のチャネルを含む1つの信号経路51によって相互に結合される、少なくとも2つの信号ポート12,14と、シャントFET46のチャネルを含み、グラウンドに結合される1つのシャント経路とを備えるスイッチにおいて、前記シリーズFET42のゲートおよびシャントFET46のドレイン−ソース間に、1つの制御電圧Vを印加する。  (もっと読む)

(もっと読む)

1 - 6 / 6

[ Back to top ]