Fターム[5J056AA19]の内容

論理回路 (30,215) | 回路の種類 (3,583) | インターフェース、レベルシフト、レベル変換 (1,016) | その他から (3)

Fターム[5J056AA19]に分類される特許

1 - 3 / 3

レベルシフト回路

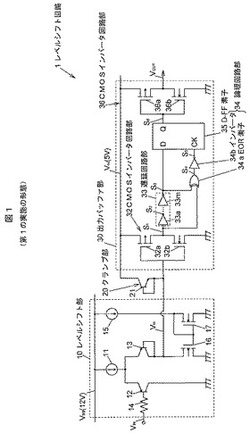

【課題】占有面積が小さく、温度変化や素子のバラツキの影響を受け難く、さらに、ノイズを低減することで高品位のレベルシフトを実現することができるレベルシフト回路を提供する。

【解決手段】レベルシフト回路1は、主に、第1の信号(VIN)をレベルシフトして第2の信号(Vm)を出力するレベルシフト部10と、pMOSトランジスタ32aとnMOSトランジスタ32bを含み、第2の信号を反転させた第3の信号(S1)を出力するCMOSインバータ回路部32、偶数個のインバータ素子(第1のインバータ33a〜第mのインバータ33m)を含み、第3の信号を遅延させた第4の信号(S3)を生成する遅延回路部33、論理素子を含み、第3の信号及び第4の信号が入力して第5の信号(S5)を出力する論理回路部34、及び第4の信号と第5の信号が入力するD−FF素子35、を含む出力バッファ部30と、を備える。

(もっと読む)

半導体集積回路装置

【課題】 差動増幅回路の出力信号の特性を改善する。

【解決手段】入力データ信号が‘Low’レベルになると、トランジスタ16に流れる電流I1の電流が減少し、抵抗14と抵抗14aとの接続部(ノードD)の電位が高くなる。この電位は、トランジスタ18にゲートに入力(負帰還)され、該ゲート電位が高くなることによって、テイル電流量I_TAILが増加する方向に調整される。入力データ信号が‘High’レベルになると、電流I1の電流が多く流れ、ノードDの電位が下がる。これによって、トランジスタ18のゲート電位(負帰還)が下がり、テイル電流量I_TAILを絞る方向に調整される、これによって入力波形の立上りと立下りとで、それぞれ出力波形との遅延時間の差が小さくなる。

(もっと読む)

集積回路の制御電圧決定方法、TEG回路のゲート電圧決定方法、TEG回路試験方法及び試験装置

【課題】集積回路において、トランジスタのしきい値電圧などの特性変動あるいはばらつきが与える回路動作への影響を受けにくい集積回路およびTEG回路を提供する。

【解決手段】1対の抵抗デバイスMP1,MP2と、1対のN型差動トランジスタMN1,MN2と、該1対のN型差動トランジスタに動作電流を供給する電流源トランジスタMLとを備えた電流モード動作回路において、その電流源トランジスタに流れる電流の制御電圧VLを、N型差動トランジスタのしきい値電圧などの特性変動に対して、集積回路の電圧利得が少なくとも1以上となるよう決定する。

(もっと読む)

1 - 3 / 3

[ Back to top ]