Fターム[5J056DD24]の内容

論理回路 (30,215) | 構成要素(素子) (5,667) | トランジスタ(UJT、IGBT他) (4,294) | トランジスタの組合せ (2,266) | PnPトランジスタのみ (3)

Fターム[5J056DD24]に分類される特許

1 - 3 / 3

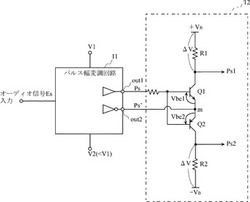

スイッチングアンプ及びそのスイッチングアンプのレベルシフト回路

【課題】所定の振幅範囲でレベルが変化するPWM信号から振幅範囲の異なるPWM信号に変換するレベルシフト回路の簡単化を図る。

【解決手段】スイッチングアンプはオーディオ信号EsをPWM信号に変換して出力するパルス幅変調回路11の後段にシフトレベル回路12が設けられる。パルス幅変調回路11はPWM信号PsとPWM信号Psに対して逆相関係のPWM信号Ps’を出力する出力端子out1,out2を有する。シフトレベル回路12を抵抗R1、P型トランジスタQ1、N型トランジスタQ2および抵抗R2がこの順で直列接続された回路で構成し、この回路の両端を電源電圧+VB,−VBが入力される一対の電源端子に接続し、トランジスタQ1,Q2のベースにパルス幅変調回路11のout1を接続し、トランジスタQ1,Q2の接続点mにパルス幅変調回路11のout2を接続する構成とした。

(もっと読む)

インターフェース回路

【課題】入力部3の入力信号S1を制御部2に入力するものにあって、入力部3と制御部2との間に接続された抵抗素子R3の発熱を防止することで、抵抗素子R3の耐久性を向上させる。

【解決手段】制御部2に接続された入力部3の入力信号S1を入力インターフェース部4を介して制御部2に入力するようにした入力インターフェース回路1において、入力部3と制御部2との間に接続された抵抗素子R1の発熱を防止すべく、入力部3からの入力信号S1を間欠的に制御部2に入力させる間欠入力手段5が設けられている。

(もっと読む)

オンダイターミネーション回路

【課題】ターミネーション抵抗値を調整する場合に、高周波領域においても、ターミネーション抵抗値を目標値に近い値に維持し、かつ寄生素子構成が異なることによりターミネーション抵抗値が変動することを抑制する。

【解決手段】本発明のオンダイターミネーション回路は主抵抗回路Aと調整回路Bとを有している。主抵抗回路Aは、オンダイターミネーション回路をオフ状態とする場合にオフされオン状態とする場合にオンされるトランジスタp1と、抵抗素子r0とを備える。調整回路Bは、オンダイターミネーション回路をオン状態として当該オンダイターミネーション回路全体のターミネーション抵抗値を調整する場合にオンまたはオフされ、主抵抗回路Aと並列に接続されるとともに互いに並列に接続されるトランジスタp2〜p5を備える。

(もっと読む)

1 - 3 / 3

[ Back to top ]