Fターム[5J079FB07]の内容

電気機械共振器を用いた発振回路 (23,106) | 回路要素 (2,263) | 記号の可変電流源 (5)

Fターム[5J079FB07]に分類される特許

1 - 5 / 5

水晶発振器

【課題】電源電圧が低電圧化されても安定した発振動作が可能な水晶発振器を提供する。

【解決手段】本発明の水晶発振器は、高電位側電源と水晶振動子(2)の一端並びに他端との間に設けられた第1,第2の抵抗(R1,R2)と、その一方の主端子が前記水晶振動子の一端並びに他端と接続された第1,第2のトランジスタ(T1,T2)と、第1,第2のトランジスタの他方の主端子間に接続されたキャパシタ(C1)と、第1,第2のトランジスタの他方の主端子と低電位側電源との間に設けられた電流源(IR1,IR2)又は抵抗と、第1,第2のトランジスタの一方の主端子と第2,第1のトランジスタの制御端子との間に設けられ、一方の主端子の電圧に追従するとともに一方の主端子の電圧から直流オフセット電圧分降下した電圧を生成して制御端子に印加させる第1,第2の電圧フォロワ回路(4,5)と、を備える。

(もっと読む)

水晶発振装置および半導体装置

【課題】低負荷容量値対応の水晶振動子を十分に適用することが可能な水晶発振装置を提供する。

【解決手段】例えば、配線基板PCB上に、発振入力信号XIN用の配線パターンLN_XINと、発振出力信号XOUT用の配線パターンLN_XOUTを設け、その間の領域に接地電源電圧VSS用の配線パターンLN_VSS1bを配置する。LN_XINとLN_XOUTの間には水晶振動子XTALを接続し、その負荷容量となる容量Cg,Cdの一端をLN_VSS1bに接続する。更に、これらの配線パターンを囲むようにVSS用の配線パターンLN_VSS1aを配置し、加えて、下層にもVSS用の配線パターンLN_VSSnを配置する。これらによって、XINノードとXOUTノード間の寄生容量の低減や、当該ノードのノイズ耐性の向上等が可能になる。

(もっと読む)

圧電発振器

【課題】圧電発振器にスリープモードを備える。

【解決手段】圧電振動子100を発振させた発振信号Vpを出力する発振回路110と、発振回路110に電流Idを供給する電流源回路120と、発振回路110から出力された発振信号Vpを整形した出力信号OUTを出力するバッファ回路130と、スリープモードとノーマルモードとを切り替える制御信号SLを入力する制御端子140と、を含み、電流源回路120は、制御信号SLがスリープモードの時はノーマルモードの時に比べて発振回路110に供給する電流Idが少なくなるように切り替える第1の切替部124を含み、バッファ回路130は、制御信号SLがスリープモードの時はバッファ回路130を構成する素子への電流の供給を止める第2の切替部132と、制御信号SLがスリープモードの時は発振信号Vpが出力されないように切り替える第3の切替部133と、を含む圧電発振器1。

(もっと読む)

発振回路及び発振器

【課題】定常時の負性抵抗と比較して起動時の負性抵抗が十分に大きな発振回路及び発振器を提供すること。

【解決手段】振動子を発振させる発振回路は、1つのトランジスタを有するインバータと、インバータと並列に接続された帰還抵抗と、インバータの入力側及び出力側のそれぞれに設けられた容量素子と、レベルが異なる2種類の電流のいずれかをインバータに供給する可変電流源と、発振回路の電源の起動から所定時間をカウントするタイマ回路と、可変電流源が供給し得る2種類の電流の内、タイマ回路によるカウント時間が所定時間を経過するまでの間はレベルが大きい方の電流を、所定時間を経過した後はレベルが小さい方の電流をインバータに供給するよう可変電流源を制御する電流制御部とを備える。

(もっと読む)

低ノイズ且つ高安定性を実現するクリスタルオシレータ

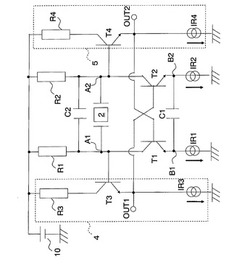

【課題】振幅が制御された差分信号を出力すると共にDCレベルを制御する、低ノイズ且つ高安定なクリスタルオシレータを実現する回路、方法および装置を提供する。

【解決手段】クリスタルオシレータ回路であって、フィードバックループを2つ有する。一方はクリスタルオシレータ信号のDCレベルを設定するために用いられ、他方はクリスタルオシレータ信号の振幅を調整するために使用される。DCレベル設定フィードバックループは、オシレータ信号のDC成分を2つの供給電圧の間に収まるように設定することができる。振幅制御ループは、クリスタルオシレータの出力信号の振幅を一定の範囲内に収める。振幅は、供給電圧をクリッピングすることなく安定性を高めジッタを低減することができる範囲内でスイングが最大となるように設定することができる。振幅制御回路は、ノイズ性能を改善するべくデジタル回路としてもよい。上記2つのループの時定数は、不安定化を避けるために分離してもよい。

(もっと読む)

1 - 5 / 5

[ Back to top ]