Fターム[5J106DD04]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 波形・レベル変換回路 (375) | リミッタ (3)

Fターム[5J106DD04]に分類される特許

1 - 3 / 3

チャージポンプ及びPLL回路

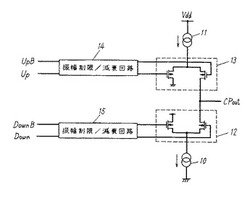

【課題】チャージポンプ回路のスイッチングトランジスタを大振幅の制御信号で駆動すると、ソース、ドレインの寄生容量、ゲート電極下のチャンネル電荷により、出力電流に乱れが生じる。特にチャージポンプの出力電流が小さい場合顕著になる。

【解決手段】電流源10,11の出力をスイッチングするための差動構成の差動スイッチング回路12,13を設け、差動スイッチング回路12,13を構成するトランジスタのゲートにかかる論理振幅を振幅制限/減衰回路14,15を用いて小さくすることで、寄生容量、チャンネル電荷による出力電流の乱れを改善する。

(もっと読む)

オフセット位相同期ループのベースバンド補償の方法と装置

位相変調器はオフセット位相同期ループ(OPLL)の増加された帯域幅により過度のノイズを通過させること無しにOPLLを使用してより高い周波数変調を忠実に再現する。直交変調器は通過域IF信号の上にベースバンド信号からの情報を変調し、そしてリミッタが振幅変動を取り除く後に、OPLLはRF信号上で位相変調を再現する。OPLLは変調周波数でリニアに変化せず、必然的に補償されない時にひずみを引き起こす群遅延を持ち込む。ベースバンドフィルタはベースバンド信号の振幅をフィルタし、OPLL群遅延を補償する相補的な群遅延を持ち込み、そしてベースバンドフィルタ、直交変調器、リミッタおよび変調周波数が変化する時に実質的に一定のままであるOPLLの総合群遅延という結果になる。OPLL群遅延を補償することはRF信号の搬送周波数からオフセット周波数でのひずみとスペクトルエネルギーとを減少させる。  (もっと読む)

(もっと読む)

遅延ロックループ

【課題】 同期保持範囲が狭く、同期点が範囲外になると同期外れを引き起こす。この状態では制御が効かなくなり、偶発的な復帰するのを待つほかなく復帰に時間を要した。同期精度を向上させるためには回路規模の増大を招いた。

【解決手段】 入力信号が周期fcのパルス信号の際、LC共振回路11に入力されると周期成分fcが抽出されて出力される。パルス発生器2から同期点に位相を合わせた50%デューティのパルスを出力するよう設定し、乗算器14で共振回路出力12と乗算する。乗算器14の出力は、同期ループが遅れているときはプラス、進んでいるときはマイナスになる。この信号を加算器15で加算し、ループフィルタ9へ積分してVCO10へフィードバックし、発信周波数を制御することで同期ループがロックする。その結果乗算器14の出力はゼロ(プラス/マイナス)となりフィードバックループが安定し、同期状態が保持される。

(もっと読む)

1 - 3 / 3

[ Back to top ]