Fターム[5J106EE13]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−付属構成 (846) | 表示回路 (3)

Fターム[5J106EE13]に分類される特許

1 - 3 / 3

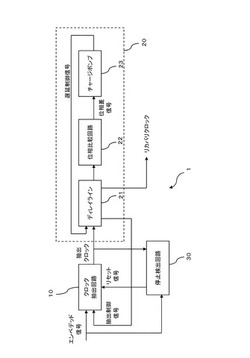

クロック発生回路、表示装置用駆動回路及びクロック発生回路の制御方法

【課題】電源投入時や通常動作時でも、より確実にクロックの生成が停止した状態から回復することが可能となるクロック発生回路を提供する。

【解決手段】クロック発生回路1は、クロックとデータとが重畳されたエンベデッド信号から抽出クロックを抽出するクロック抽出回路10と、前記エンベデッド信号と前記抽出クロックとに基づき前記抽出クロックの停止を検出し、前記クロック抽出回路を初期状態にリセットするリセット信号を出力する停止検出回路30と、を備えるものである。

(もっと読む)

信号処理装置

【課題】 外部からの基準信号の周波数変化が安定している状態であるかどうかをユーザが容易に判別可能とする。

【解決手段】 外部機器から供給された基準信号を入力する入力手段と、前記入力手段により入力された基準信号とクロックとの位相差を検出する位相検出手段と、前記位相検出手段の出力に応じた周波数の前記クロックを発生する発生手段と、前記位相検出手段の出力に基づいて前記入力手段により入力された基準信号の周波数と前記クロックの周波数との誤差を検出し、前記検出した誤差に基づいて前記基準信号の周波数変化の状態を示す情報を表示装置に表示する制御手段とを備える。

(もっと読む)

集積回路、表示装置及びそれを用いた電子機器

【課題】DLLに求められる保証動作周波数帯域を低め、基準クロック信号が二逓倍された周波数をそれぞれ有し、位相差のある2つのクロック信号を生成することができる集積回路、表示装置及び電子機器を提供する。

【解決手段】タイミングコントロールICは、一周期Tの基準クロック信号ICLKと同一周波数の第1〜第4のクロック信号CLK1〜CLK4であって、第N(N=1,3のいずれか)のクロック信号に対する第(N+1)のクロック信号の位相遅れが位相差T/4で、かつCLK1に対するCLK3の位相遅れが位相差α(0<α<T/4)であるCLK1〜CLK4のクロック信号を発生させるDLL40と、CLK1が二逓倍されたデータ生成用のCLK5を生成し、かつ、CLK3が二逓倍されて、CLK5に基づき生成されデータ信号に対して位相差αの遅れで同期したCLK6を生成する二逓倍回路50とを有する。

(もっと読む)

1 - 3 / 3

[ Back to top ]