Fターム[5K034HH43]の内容

通信制御 (28,107) | 通信処理機能 (5,992) | 転送速度の変換、バッファリング (1,349) | バッファの書込み、読出し制御 (616) | 書込み、読出し信号 (65)

Fターム[5K034HH43]の下位に属するFターム

書込み、読出し指令 (14)

書込み、読出しクロック (10)

アドレスによるもの (32)

Fターム[5K034HH43]に分類される特許

1 - 9 / 9

音声通信装置及びプログラム

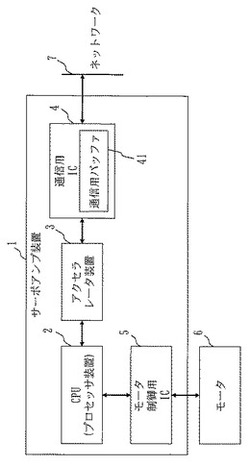

アクセラレータ装置及びサーボアンプ装置

【課題】通信用バッファからデータを読み出す際のCPUのアクセス時間を短縮し、CPUの処理効率を改善する。

【解決手段】アクセラレータ装置3が、CPU2の読み出しタイミングに先立って通信用バッファ41からデータを読み出し、CPU2の読み出しタイミングが到来すると予め読み出しているデータをCPU2に出力するため、CPU2はデータ読み出し速度が遅い通信用バッファ41からデータを読み出す必要がなく、CPU2のアクセス時間を短縮し、CPU2の処理効率を改善することができる。

(もっと読む)

待ち時間に無感覚なFIFOシグナリングプロトコル

【課題】ファーストインファーストアウト(FIFO)の満杯レベルおよび/またはFIFOの書き込みステータスについての情報を送信領域またはソース領域に供給する。

【解決手段】第1のデータレートで動作するソース領域からのデータは、異なるデータレートで動作する別の領域内のFIFOに転送される。ソース側カウンタは、FIFOにおいて利用可能なスペースを追跡する。イニシャルカウンタ値はFIFOの深さに相当する。カウンタはソース領域からのデータレディ信号に応答してデクリメントする。カウンタはFIFOからのデータのリードのシンク領域からのシグナリングに応答してインクリメントする。FIFOが満杯であることをカウンタが示すとき、ソースは、もうひとつのデータのビートを送信し、FIFO位置が利用可能になるまでデータの最後のビートは連続的にソースから送信され、効率的にもうひとつのFIFO位置を提供する。

(もっと読む)

データ送信装置とデータ受信装置及びデータ送受信方法

【課題】受信側において、表示時刻等の再生時刻に遅れたパケットを破棄せずに保存することができ、また、再送パケットによる伝送帯域の無駄な使用を抑制すること。

【解決手段】受信バッファ102に受信パケットを保存し、再生判定手段103で、その保存パケットが再生時刻に間に合うか否かを判定し、間に合うと判定された保存パケットの再生順序及び保存アドレスを再生用ポインタ104に記憶し、この再生用ポインタ104に従い保存パケットを読み出して再生する。また、保存用ポインタ106に、保存パケットの再生順序及び保存アドレスを記憶し、メディア変換手段107で、保存用ポインタ106に従い保存パケットを読み出し、保存メモリ108に記憶可能な形式に変換して記憶する。

(もっと読む)

信号転送装置及び信号転送方法

【課題】この発明は、バスの混雑状況に影響されることなく、映像や音声等の信号に対して、より正確にその転送開始時刻にDMA転送を開始させることができるようにした信号転送装置及び信号転送方法を提供することを目的としている。

【解決手段】映像ストリームとその転送開始時間を含む時間情報とに対してそれぞれ識別子付きのディスクリプタを作成し、ディスクリプタ、時間情報及び映像ストリームをメモリ16に記録する。メモリ16からディスクリプタを順次読み取って、メモリ16から映像デコーダ18に映像ストリームの転送を行なう際に、時間情報を示すディスクリプタを読み取ったとき、その時間情報に基づいて映像ストリームの転送を制御する。

(もっと読む)

データ転送システム、受信バッファ装置、データ転送システムの仕様設定方法及び画像形成システム

【課題】 LSIのチップサイズの小型化によりコストダウンを図りつつ、転送レートが低下することのないシリアルデータ転送を可能にする。

【解決手段】 データ転送される転送パケットデータのペイロードサイズとデータ受信部或いはスイッチが備える受信バッファ装置の受信バッファサイズとの比率が、受信バッファサイズに対して2つのペイロードサイズが入る関係を有する場合には、比率が1の場合に比べて転送レートをよくすることができる。受信バッファサイズに対して2つのペイロードサイズが入る関係の場合であれば、それほど受信バッファサイズを大きくすることがなく、LSIのチップサイズの小型化によりコストダウンを図ることもできる。

(もっと読む)

受信データ格納装置及び受信データ格納方法

【課題】 小形・簡便・低コストで転送効率が高い受信データ格納装置及び受信データ格納方法を提供する。

【解決手段】 ネットワークからの受信パケットデータに対する付加情報データを生成する情報付加回路と、前記受信パケットデータと前記付加情報データとを一次的に格納するバッファと、前記バッファに格納されたデータをメインメモリにストア&フォワード方式で転送するデータ転送制御回路とを備える受信データ格納装置において、前記バッファは、切れ目のないアドレスで形成され、前記データを格納するリングメモリと、前記リングメモリを制御するリングメモリ制御回路とを備え、前記リングメモリ制御回路は、前記受信パケットデータを順次プッシュするアドレスを指定するライトポインタと、前記付加情報データをプッシュする所定のアドレスを指定し、読出し可能なアドレスを指定するリード許可ポインタと、前記メインメモリに対して順次ポップするアドレスを指定するリードポインタとを有することを特徴とする受信データ格納装置。

(もっと読む)

メディアコンバータ

【課題】 伝送速度がギガビットクラスのメディアコンバータに関し、簡単な構成によりフレームロスの発生を回避する。

【解決手段】 フレーム伝送に於ける電気信号データと光信号データとの間の変換手段を含むメディアコンバータであって、電気信号フレームの伝送側の物理層終端部3と、光信号フレームの伝送側の物理層終端部4と、転送データを処理する主信号処理部1,2とを含み、主信号処理部1,2は、メモリ部7と、このメモリ部7に対する書込み及び読出しを制御するメモリ制御部8と、メモリ部7に書込むフレームが奇数バイトか偶数バイトかを識別して、フレーム間時間を奇数バイトのフレームに対しては奇数バイト分、偶数バイトのフレームに対しては偶数バイト分とする読出タイミングを生成して、メモリ制御部8に加えるフレーム読出タイミング生成部9とを備えている。

(もっと読む)

記憶装置

【課題】本発明は、任意のデータ長を有するデータの入力を受けてそのデータを記憶し、その記憶したデータを入力順に出力する記憶装置に関し、データ領域に記憶された、任意のデータ長を有するデータの領域解放処理を高速に実行することのできる記憶装置を提供することを目的とする。

【解決手段】データの入力によってライトポインタ12のライト位置が変更される度に、変更前のライト位置を追加的に保存する開始位置ポインタ15を備えており、領域解放の際には、保存されたライト位置と、解放されるデータ数とに基づいて新たなリード位置が求められる。

(もっと読む)

1 - 9 / 9

[ Back to top ]