Fターム[5K034HH44]の内容

通信制御 (28,107) | 通信処理機能 (5,992) | 転送速度の変換、バッファリング (1,349) | バッファの書込み、読出し制御 (616) | 書込み、読出し信号 (65) | 書込み、読出し指令 (14)

Fターム[5K034HH44]に分類される特許

1 - 14 / 14

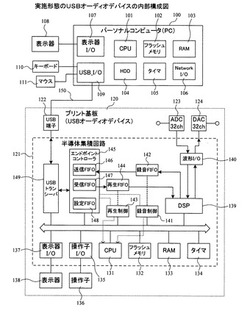

オーディオデータ入力装置および出力装置

【課題】USB等の規格で接続するオーディオデータの入力装置や出力装置において、低速で処理能力の低いCPUであってもストリーミングによるデータ転送が実現できるようにすることを目的とする。

【解決手段】所定のフレーム周期毎の処理でオーディオデータを転送するオーディオデータ出力装置および入力装置において、該フレーム周期毎の処理をCPU以外のハードウェアで実施し、CPUにはフレーム周期毎の割込がかからないようにする。ホストからオーディオデータ出力装置へのオーディオデータの転送の場合は、再生制御部の制御により受信バッファおよび再生バッファに係るデータ転送の制御と、受信部および処理部(DSP)の制御を行う。オーディオ出力装置からホストへのオーディオデータの転送の場合は、録音制御部の制御により送信バッファおよび録音バッファに係るデータ転送の制御と、送信部および処理部の制御を行う。

(もっと読む)

バッファ制御方法およびバッファ制御装置

【課題】内部バッファの容量の削減を行う。

【解決手段】内部バッファと外部バッファに蓄積されたデータ量の和を計測し、データ量が所定の閾値を上回った場合に閾値フラグをAとし、所定の閾値を下回った場合に閾値フラグをBとする判断処理手段と、閾値フラグがAの場合に外部バッファに起動指示を行い、閾値フラグがBかつ外部バッファが空の場合に外部バッファに停止指示を行う外部バッファ起動指示制御処理手段と、閾値フラグがB/Aの場合に入力パケットの蓄積先を内部バッファ/外部バッファに決定する蓄積先制御処理手段と、入力パケットの蓄積先に従って、入力パケットを内部バッファ/外部バッファに蓄積する蓄積制御処理手段と、入力パケットの蓄積先とパケット長を管理する蓄積情報管理処理手段と、蓄積情報管理処理手段で管理される情報に従い、内部バッファ/外部バッファのいずれか一方からパケットを出力する読み出し制御処理手段とを備える。

(もっと読む)

無線データ通信方法

【課題】送信側手段から送信される信号をリングバッファメモリに順次保存してパケット送信し、受信側手段にて復元することにより、到達したデータから、未到達のデータも復元できる無線データ通信方法を提供することである。

【解決手段】計測器30から送信側手段20へデータを送出するステップと、送信側制御手段21は、計測器から入力されたデータをリングバッファメモリ26の書込みポイントへ保存すると共に制御情報を更新し、所定数のデータが更新される毎に、リングバッファメモリのデータ及び制御情報をパケット送信するステップと、受信側手段40は、送信側手段から送信されたパケットを受信し、受信側制御手段41にて、受信したパケットに含まれる制御情報に基づいて、パケット中の更新されたデータを読み出してリングバッファメモリ46に上書きし、展開してリングバッファメモリに保存するステップと、を有する。

(もっと読む)

映像配信システム、映像配信装置、映像受信装置、映像配信方法、映像受信方法及びプログラム

【課題】階層符号化されたコンテンツを配信する映像配信システムにおいて、映像受信装置から映像配信装置に対してバッファの利用状況を通知することなく、映像コンテンツの配信開始時に映像が表示されるまでの待ち時間を短縮させる。

【解決手段】配信データ量検出手段106は、基本レイヤデータの配信量を検出する。配信速度決定手段106は、配信開始時から配信データ量検出手段107によって検出された配信データ量が目標量に達するまで、基本レイヤデータの配信ビットレートをそのエンコードビットレートよりも大きな値に決定する。また、目標量に達した後は、基本レイヤデータおよび各拡張レイヤデータの配信ビットレートをそれぞれその信号のエンコードビットレートに応じた値に決定する。

(もっと読む)

画像伝送装置

【課題】画像伝送装置において、一時的な伝送路の障害に対しても画像符号化データを最適な状態で伝送可能とする。

【解決手段】プロトコル制御部132は、設定されている要求間隔に従ってパケットデータを要求する複数のタイマー処理部139、および伝送路の破棄率情報と上記要求間隔に加算する遅延時間との関係を示すテーブルを記憶したメモリを有し、上記複数のタイマー処理部の各々は、それぞれの画像受信部からのパケットデータの送信要求があると、上記テーブルから上記画像受信部から送られてくる破棄率情報に対応する遅延時間を求めて、該遅延時間を上記要求間隔に加算し、加算された要求間隔の経過後に上記パケット処理部137を介してバッファ133からパケットデータを読み出し、上記要求のあったそれぞれの上記伝送路に伝送する。

(もっと読む)

パケットバッファFIFOメモリ装置

【課題】受信したパケットのパケットサイズが異常な値を示したときにも正常な動作をするパケットバッファ用FIFOメモリを提供する。

【解決手段】順次供給されるパケットデータについてメモリへの書き込み及びメモリからの読み出しをFIFO制御の下で行うパケットバッファFIFOメモリ装置である。書き込みパケットデータについて書き込みアドレスを指定しつつメモリへの書き込みをなす書込み手段と、読み出しアドレスを指定しつつメモリからパケットデータを順次読み出す読出し手段と、書込み手段と読出し手段についてFIFO制御をなす状態制御手段と、を含む。書込み手段は、書き込みパケットデータに対して監視フラグを挿入する監視フラグ挿入手段を含み、読出し手段は、メモリからパケットデータを読み出しつつ読み出されたパケットデータから監視フラグを抽出して当該抽出された監視フラグのビット値が期待値とは異なる場合に異常と判定する異常判定手段を含む。

(もっと読む)

帯域制限回路及びネットワーク中継装置

【課題】ベストエフォート方式と帯域固定方式とを切り替え可能で、帯域固定方式を用いる際に通信を瞬断させることなく設定帯域を変更可能な帯域制御回路及びこれを用いたネットワーク中継装置を提供する。

【解決手段】基準時間情報を生成する基準カウンタ11と、基準時間情報によって示される期間内に読み出されたデータ量を計測する積算カウンタ12とを備え、積算カウンタ12によって計測されたデータ量が所定量に到達した場合に、積算カウンタ12の値がリセットされ、帯域固定方式での通信時、FIFO1又は2からのデータ読み出し中に読み出したデータの積算量が所定量を超えた場合、該所定値を超過したデータ分だけ次回のデータ読み出し時の所定値を小さくする。

(もっと読む)

映像データの処理方法及び無線通信装置

【課題】映像の乱れを抑制出来る映像データ処理方法及び無線通信装置を提供すること。

【解決手段】無線通信によって受信した映像データを遅延時間の経過後に再生し、且つ前記映像データを前記遅延時間に相当する数だけ蓄積するバッファメモリ21を備えた無線通信装置8による映像データの処理方法であって、カウンタ24がカウントを開始するステップS13と、タイムスタンプが付与された前記映像データを受信するステップS10と、前記バッファメモリ21内の前記映像データ数が閾値よりも低い場合、前記タイムスタンプとカウンタ値とを比較するステップS21と、前記タイムスタンプが前記カウンタ値よりも小さい場合に当該映像データを破棄し、大きい場合に前記バッファメモリに蓄積するステップS18、S22とを具備し、前記カウンタ24は、前記タイムスタンプよりも前記遅延時間だけ前の時刻に相当する値からカウントを開始する。

(もっと読む)

通信装置および通信方法

【課題】低遅延でのRDMA通信を実現する。

【解決手段】パケット受信部81でのパケット識別後、パケットエラーチェック部83でのエラー判定と平行して、コネクション情報の読み出し、ペイロードの書込位置の特定、アプリケーションメモリ領域のペイロード書込処理を実施することにより、エラー判定結果を待たずに、ペイロード書込を開始することで低遅延でのRDMA通信を実現する。また、エラー検出時には、上書きされた有効データを無効領域として管理することで、再送されてきたパケットのペイロードの格納先が過去に受信したパケットのペイロードの格納先と一部もしくは全てが重なってしまう可能性があるTCP等のレイヤ4プロトコルを利用する場合であっても、アプリケーションに破壊されたデータが渡されないようにする。

(もっと読む)

伝送制御装置およびサンプリング周波数変換装置

【課題】FIFOを用いた非同期伝送を行う伝送制御装置であって、ジッタに起因したFIFOの残存データ量の変動に即応して残存データ量を速やかに適正値に収束させる伝送制御装置を提供する。

【解決手段】FIFO10は、入力データを書き込みアドレスにより指定されるエリアに記憶し、読み出しアドレスにより指定されるエリアに記憶されたデータを出力する。書き込み制御部30は、mビットからなる入力位相情報を更新し、入力位相情報における上位jビット(j<m)からなるビット列を書き込みアドレスとしてFIFO10に供給する。読み出し制御部40は、mビットからなる出力位相情報を更新し、出力位相情報における上位jビットからなるビット列を読み出しアドレスとしてFIFO10に供給する。PLL80は、読み出し要求信号RRに応じて変化する出力位相情報に位相同期して入力位相情報が更新されるように入力位相情報の更新速度を制御する。

(もっと読む)

受信データ格納装置及び受信データ格納方法

【課題】 小形・簡便・低コストで転送効率が高い受信データ格納装置及び受信データ格納方法を提供する。

【解決手段】 ネットワークからの受信パケットデータに対する付加情報データを生成する情報付加回路と、前記受信パケットデータと前記付加情報データとを一次的に格納するバッファと、前記バッファに格納されたデータをメインメモリにストア&フォワード方式で転送するデータ転送制御回路とを備える受信データ格納装置において、前記バッファは、切れ目のないアドレスで形成され、前記データを格納するリングメモリと、前記リングメモリを制御するリングメモリ制御回路とを備え、前記リングメモリ制御回路は、前記受信パケットデータを順次プッシュするアドレスを指定するライトポインタと、前記付加情報データをプッシュする所定のアドレスを指定し、読出し可能なアドレスを指定するリード許可ポインタと、前記メインメモリに対して順次ポップするアドレスを指定するリードポインタとを有することを特徴とする受信データ格納装置。

(もっと読む)

シリアル通信回路

【課題】 外部機器との接続状態が未接続であっても、バッファに処理データが蓄積されることを防止することができ、マルチタスクで行われる他の処理への影響をなくすことができるシリアル通信回路を提供する。

【解決手段】 バッファ11は、外部機器2へ送信するデータを蓄積し、データ送信部12は、バッファ11によって蓄積されたデータを外部機器2へ送信し、クロック信号検知回路14は、外部機器2から入力されるクロック信号を検知し、データ消去部16は、クロック信号検知回路14によってクロック信号が検知されない場合、バッファ11に蓄積されているデータを消去する。

(もっと読む)

デジタル遅延バッファ及びこれに関連する方法

【課題】 従来の技術に関連する待ち時間遅延に陥ることなく配列データストリームを生成するために、到着する要素間での過度の遅延の影響を制御する。

【解決手段】 デジタル遅延バッファが、高速処理・小容量メモリ部及び低速処理・大容量メモリ部双方に提供される。2つのメモリ部を使用することによって、たとえ1つの部分が過度の遅延を受けても、バッファがnビットブロックレベルの待ち時間で複数の遅延されたデータ部分から配列データストリームを生成することを可能とする。

(もっと読む)

ライン遅延生成回路

【課題】 m個のライン遅延データを出力するためには2ポートメモリであるFIFOをm個カスケード接続する必要があり、FIFOメモリ2が大型化してしまうなどの課題があった。

【解決手段】 パケット化回路11により生成されたパケットデータのライト指令を1ポートSDRAM13に出力するとともに、現在格納しているパケットデータ(ライン遅延データ)のうち、任意のライン遅延データのリード指令を1ポートSDRAM13に出力する。

(もっと読む)

1 - 14 / 14

[ Back to top ]