Fターム[5L106DD08]の内容

半導体メモリの信頼性技術 (9,959) | 試験 (2,465) | スキャンパス (93)

Fターム[5L106DD08]に分類される特許

1 - 20 / 93

半導体記憶装置

【課題】

実施形態は、解析が簡便な半導体記憶装置を提供する。

【解決手段】

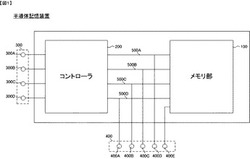

本実施形態の半導体記憶装置は、メモリ部(100)と、前記メモリ部(100)に接

続されるコントローラ部(200)と、前記コントローラ部(200)に接続される第1

入出力部(300)と、前記メモリ部(100)と前記コントローラ部(200)の間の

ノードに電気的に接続され、前記第1入出力部(300)とは異なる第2入出力部(40

0)とを備える。

(もっと読む)

集積回路装置および集積回路装置の試験方法

【課題】メモリへの連続アクセス回数を増やしても使用するスキャンチェーン数を増加させることなく試験を行うことができる集積回路装置の提供を図る。

【解決手段】メモリMEMと、該メモリに接続される複数のロジック回路Lと、前記メモリおよび前記ロジック回路の試験を行うスキャンチェーンSCI,SCIIと、を含む集積回路装置であって、前記メモリの前段の第1スキャンチェーンSCIにおいて、前記メモリに対して出力端子が繋がっている少なくとも2つの第1および第2フリップフロップFF107,FF108を有し、前記第2フリップフロップFF108の前記出力端子と、前記第1フリップフロップFF107のスキャン入力端子の間に、少なくとも1つの第1挿入フリップフロップFF105,FF101を挿入して、前記スキャンチェーンの接続を規定する。

(もっと読む)

半導体装置及びその制御方法

【課題】階層化されたビット線構成のストレス印加テスト時に各ローカルビット線に異なるプリチャージ電圧を供給するための面積増加を抑制し得る半導体装置を提供する。

【解決手段】階層化メモリセルアレイは、グローバルビット線GBL、ローカルビット線LBL、グローバルビット線用のプリチャージ回路Q10、Q11、ローカルビット線用のプリチャージ回路Q20、階層スイッチQ30を備えている。テスト動作時には、高電位と低電位に設定したプリチャージ電圧VBLP0、VBLP1をプリチャージ回路Q10、Q11を介して各グローバルビット線GBLに印加し、かつ各ローカルビット線LBLにプリチャージ電圧VBLPLを印加せず、各階層スイッチQ30を導通させることで1対のローカルビット線LBLに異なる電位の電圧ストレスが印加される。サブアレイSARY毎にプリチャージ電圧VBLPLを2系統に分離するよりも少ない面積で実現できる。

(もっと読む)

抵抗変化メモリのテスト装置、方法および抵抗変化メモリ装置

【課題】任意のテストサイクルにおけるサイクル時間を局所的に自由に調整するとともにチップサイズ、テストコストを削減する。

【解決手段】シフトレジスタ回路の出力と第1のライトイネーブル信号とに基づき、複数のシーケンスのうちの限界時間の確認を行うシーケンスに対応して信号変化する第2のライトイネーブル信号を発生し、第1および第2のライトイネーブル信号を用いて信号変化する時間間隔が局所的に前記第1のライトイネーブル信号の周期よりも短い複数のコア制御信号を発生し、発生した複数のコア制御信号を用いて抵抗変化メモリの動作確認を行う。

(もっと読む)

半導体記憶装置

【課題】メモリセルのリーク特性、センスアンプの出力特性アンバランスの影響を排除し、メモリセルの欠陥を高効率で確実に検査可能とする。

【解決手段】行列状の複数のスタティック型メモリセル5と、行方向に並ぶメモリセルに共通に接続されたワード線WLnと、列方向に並ぶメモリセルに共通に接続され相補対を成すビット線対BLO、NBLOと、ビット線対に接続されメモリセルのデータを外部に出力するセンスアンプと、ビット線対の各々を第1プリチャージ電位に設定する第1及び第2プリチャージ回路7a、7bと、ビット線対の各々を第2プリチャージ電位に設定する第3及び第4プリチャージ回路7c、7dと、ビット線対の各々のビット線電位を外部に出力する第1及び第2検査出力部8a、8bとを備え、センスアンプからのデータ、第1または第2検査出力部からのビット線電位のうちのいずれかを選択的に出力するように制御可能である。

(もっと読む)

半導体集積回路、および被検査回路の検査方法

【課題】BIST回路を有する半導体集積回路において、長時間を要することなく、被検査回路に対して複数回検査を実行し、かつ、各回の検査結果を個別に認識可能にする。

【解決手段】例えばメモリマクロ1のような被検査回路の検査結果を、複数個記憶可能に構成された検査結果格納回路8が設けられている。検査結果格納回路8はBIST制御回路7から出力された信号BIST_GO,BIST_DONEを入力とし、モード切替信号BIST_MODEが検査モードを示すときは、信号BIST_GOが示す検査結果を信号BIST_DONEが検査終了を示す毎に格納する。そして、モード切替信号BIST_MODEが結果読み出しモードを示すときは、検査結果格納回路8は格納している検査結果を出力する。

(もっと読む)

半導体装置

【課題】データの入出力用端子のうち、一部の端子にテスト用ピンを接続することで、全ての入出力用回路の検査を可能にした半導体装置を提供する。

【解決手段】複数の外部端子と、複数のメモリセルを含むメモリセルアレイと、複数の外部端子のそれぞれに対応して、外部端子とメモリセルアレイとの間に並列に設けられた入力回路および出力回路と、検査対象の外部端子に対応して設けられた入力回路に所定のメモリセルから出力回路および外部端子を介してデータが入力されると、データに基づく信号を、検査対象の外部端子とは異なる所定の外部端子に出力する検出部とを有する。

(もっと読む)

半導体集積回路及び半導体集積回路の検査方法

【課題】メモリ及びメモリ周辺ロジック間のテストを、スキャンテストにて実現することができる半導体周期回路を提供する。

【解決手段】半導体集積回路は、メモリセル22〜25及び冗長セル26,27と、メモリセルに欠陥があった場合に冗長セルを選択するセレクタ28とを有するメモリ10と、外部からの情報に基づきセレクタに冗長セルを選択させるための第1の制御信号を生成する救済制御回路13と、救済制御回路13の第1の制御信号をラッチする救済情報保持ラッチ14と、を有する。そして、救済情報保持ラッチ14は、第2の制御信号に応じて救済制御回路13が生成した第1の制御信号をラッチする。

(もっと読む)

半導体記憶装置及びその回路の電位測定方法

【課題】大規模な半導体記憶装置における不良トランジスタの検出と、不良トランジスタの特性の測定とを高速で行うことができる、半導体記憶装置を提供する。

【解決手段】メモリ素子が縦横にマトリックス状に配列されたメモリセルアレイと、接地ノードあるいは電源ノードに接続する枝配線を有する半導体記憶装置において、電源ノードあるいは接地ノードに接続する少なくとも1つの枝配線の複数箇所に電圧測定点を接続したモニター用スイッチを有し、クロック信号に同期して前記モニター用スイッチのゲートを順に開くスイッチ選択信号発生回路を有し、前記スイッチ選択信号発生回路で選択されてゲートが開かれたモニター用スイッチを介して前記電圧測定点の電位を測定する。

(もっと読む)

半導体装置及びそのテスト方法

【課題】所望の動作周波数での高速テストが可能である半導体装置及びそのテスト方法を提供すること。

【解決手段】SiP101は、ロジックチップ103Aとメモリチップ103Bを備える。メモリチップ103Bは試験対象となるメモリ回路を備え、ロジックチップ103Aは、内部ロジック回路20と、これに電気的に接続されたテスト処理回路21とを備える。テスト処理回路21は、メモリ回路のアクセス端子と接続され、外部端子23nから入力されるテスト信号をアクセス端子に供給してメモリ回路のテストを実行するものであって、信号遅延を調整する高速テスト制御回路を有し、実動作速度での高速テストを実行する際には、外部端子23nから供給されるテスト信号を、高速テスト制御回路を介してアクセス端子に供給する。

(もっと読む)

半導体装置

【課題】半導体装置上の高速動作が可能な半導体記憶装置を実仕様周波数でも所望の動作を行うか確認する手段を提供する。

【解決手段】半導体記憶装置822と論理回路123とを有する半導体装置827において、半導体記憶装置822は2つのメモリアレイ領域802a,802bを備え、一方の出力をもう一方の入力として、かつ各々の読み出し書き込み制御が逆にできるようにして、半導体記憶装置822自体で検査できるようにする。

(もっと読む)

メモリ内部のスキャン機能支援

【課題】データを記憶するストレージアレイと、データをストレージアレイとの間で送信するアクセス回路とを備えるメモリが開示される。

【解決手段】アクセス回路は、データをストレージアレイへ入出力するデータ経路を形成する。アクセス回路は、第1のクロック信号の第1の位相に応答してラッチするラッチと、第2のクロック信号の第2の位相に応答してラッチし、出力ラッチを備えるラッチとを備え、第1および第2のクロック信号が互いに同期している。メモリはマルチプレクサとスキャン入力とスキャンイネーブル入力とをさらに備え、マルチプレクサがスキャンイネーブル信号に応答して、マスタ・スレーブ・フリップフロップを形成するラッチを備えるスキャン経路を形成し、スキャンイネーブル信号がアサートされている間に、スキャン入力で入力されたスキャンデータがマスタ・スレーブ・フリップフロップを通過し、出力ラッチによって出力される。

(もっと読む)

半導体記憶装置及びそのテスト方法

【課題】パーシャルアレイセルフリフレッシュ機能を高速にテストする。

【解決手段】メモリセルアレイ20内の複数の領域のうち、セルフリフレッシュ動作を行わない領域を示すマスク情報MASKを格納するマスク情報格納回路36と、セルフリフレッシュコマンドによって活性化され、リフレッシュアドレスRefADDとマスク情報MASKとの一致を検出したことに応答して一致信号HITを生成するマスク判定回路34と、一致信号HITの活性化に応答してセルフリフレッシュ動作を禁止するリフレッシュ動作制御回路35とを備える。マスク判定回路34は、テストモード信号TSETが活性化している場合には、オートリフレッシュコマンドによっても活性化される。これにより、実際にセルフリフレッシュモードにエントリすることなくパーシャルアレイセルフリフレッシュ機能のテストが行える。

(もっと読む)

半導体評価回路

【課題】不良トランジスタの検出と、不良トランジスタのトランジスタ特性の測定を高速で行うことができる、大規模な半導体評価回路(DMA−TEG等)を提供する。

【解決手段】本発明の半導体評価回路においては、評価セルアレイ中の測定対象トランジスタの閾値Vthの電圧が、閾値Vth電圧の正規分布曲線に対して、例えば、5σ(σは標準偏差)以内の分布から外れたものを選別する。そして、閾値Vthの電圧が5σ以内の分布から外れた測定対象トランジスタに対して、トランジスタ特性の測定を行う。

(もっと読む)

半導体集積回路、および半導体集積回路のテスト方法

【課題】RAMを備える半導体集積回路において遷移遅延故障テストを実行する際に、前段のロジック回路の出力をRAMのアドレス端子へ伝播することが可能な半導体集積回路を提供する。

【解決手段】本発明の半導体集積回路は、メモリ(100)と、メモリ(100)のアドレスを制御するアドレス信号を出力するロジック(300)と、ロジック(300)とメモリ(100)のアドレス端子との間に設けられて、ロジック(300)とメモリ(100)とにそれぞれ接続されるアドレス制御回路(200)とを備え、アドレス制御回路(200)は、ロジック(300)からメモリ(100)のアドレス端子までの間の遷移遅延故障テストを実行するか否かを決定するテスト信号を入力して、テスト信号が遷移遅延故障テストを実行するべきテストモードを示すときに、テスト信号の値に基づいて、ロジック(300)から入力するアドレス信号と、予め固定値に設定された出力信号とのいずれかをメモリ(100)のアドレス端子へ出力する。

(もっと読む)

半導体記憶装置及びその自己テスト方法

【課題】テストコストの低減に対して有利な半導体記憶装置及びその自己テスト方法を提供する。

【解決手段】半導体記憶装置は、不揮発性メモリ11と前記不揮発性メモリの入出力データを格納するバッファ13とを備える主記憶部1と、揮発性メモリを備える前記主記憶部のバッファ部2と、データ入出力ピンを有する自己テストインターフェイス50と、前記主記憶部と前記バッファ部とを制御する制御部30とを具備し、前記制御部は、前記データ入出力ピンを介して自己テストインターフェイスから前記バッファへデータを格納し(S1)、前記バッファの格納データを、前記揮発性メモリへ書き込み(S2)、前記揮発性メモリから読み出したデータを前記バッファへ格納し(S4)、前記バッファの格納データを前記自己テストインターフェイスから読み出し、判定させる(S5)。

(もっと読む)

汎用ポートをJTAGポートとして利用可能なメモリチップ

【課題】汎用ポートをJTAGポートとして利用できるメモリチップを提供することである。

【解決手段】マルチピンポートをJTAGポートとして利用するメモリチップはJTAGコントローラ、少なくとも1つの内部ブロック及び構成ユニットを備え、構成ユニットにより、そのチップのマルチピンポートの1つの4ピンが選択的に構成され、JTAGデータがJTAGコントローラに或いは非JTAGデータが少なくとも1つの内部ブロックに伝送される。構成ユニットは一般に永続的に、或いは変更可能に構成することができる。例えば変更可能な構成ユニットは、揮発性メモリ(VM)構成ユニットであるか、或いはプログラム可能論理デバイス(PLD)の積項出力部であることができる。

(もっと読む)

半導体記憶装置

【課題】発振回路を構成するインバータの純粋な動作速度を求めることができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のワード線と、複数のビット線と、複数のメモリセルとを含むメモリブロックと、テスト信号に基づいて制御される遅延速度調整回路が付加された発振回路と、リフレッシュモード時、発振回路の出力に基づいて複数のメモリセルを順次アクセスするアクセス制御回路と、を備える。発振回路は、テスト信号が入力されていないとき、遅延速度調整回路を有効にして第1の周期で発振し、テスト信号が入力されているとき、遅延速度調整回路を無効化して、第1の周期よりも短い第2の周期で発振する。

(もっと読む)

集積回路および試験方法

【課題】実際の動作速度でのFMB取得が可能な集積回路および試験方法の実現。

【解決手段】メモリ18と、メモリを試験するメモリ試験回路20,22-24,41と、入出力ポート11E,11Fと、を備え、メモリ試験回路の収集したメモリの出力を入出力ポートを介して出力する集積回路であって、メモリ試験回路は、メモリの出力をラッチするラッチ回路20を備え、第1クロックPLLに応じて全アドレスをアクセスするように変化させた時のメモリの出力を、第1クロックの整数倍の周期を有するラッチ信号に応じてラッチするスキャン・ラッチ動作を行い、ラッチ信号の1周期中にラッチしたデータを入出力ポートを介して出力する転送動作を行い、ラッチ回路がラッチするメモリセルのアドレス位置を変化させて、スキャン・ラッチ動作および転送動作を繰り返し、全メモリセルの出力を外部に出力する。

(もっと読む)

半導体装置およびデータ処理システム

【課題】コントロール情報の転送をデータの転送速度よりも低い周波数で動作させるモードを備える。

【解決手段】データ端子を介するデータ送受信の実行に必要なコントロール情報を、第1の動作モードでは自己のコントロール端子を介して受信し、第2の動作モードでは自己のコントロール端子と共に少なくとも一つの他のポートのコントロール端子を使用して受信する。

(もっと読む)

1 - 20 / 93

[ Back to top ]