Fターム[5L106DD14]の内容

半導体メモリの信頼性技術 (9,959) | 試験 (2,465) | 機密保護と関連するもの (10)

Fターム[5L106DD14]に分類される特許

1 - 10 / 10

半導体装置

【課題】チップ内蔵メモリのビット不良がランダムなアドレスで発生することを利用して、チップ固有IDを生成し、これを活用する手段を提供する。

【解決手段】外部からの認証要求を受けたコントローラ101は、可変電源回路102に対してメモリ103への供給電圧を通常動作時より低下させることを指示する。メモリ103への供給電圧が安定したら、コントローラ101はメモリBIST104に対してメモリテストを要求する。メモリテストの結果エラーが発生したアドレスを用いてコントローラ101は固有チップIDを作成し、認証要求の応答とする。

(もっと読む)

不揮発性半導体記憶装置のテスト方法

【課題】 冗長部カラムエリアに割り当てられた機能の合否を判定可能な不揮発性半導体記憶装置のテスト方法を提供する。

【解決手段】 不揮発性半導体記憶装置のテスト方法は、ブロックに対する動作を制限するプロテクトフラグを、制限対象とするブロック内部の所定のページに書き込むステップと、プロテクトフラグを含むページのデータを読み出し、データレジスタに転送するステップと、データレジスタに転送されたデータの内、プロテクトフラグ以外のカラムアドレス領域のデータをマスクするステップと、データレジスタ内の不良ビットを一括検知するステップと、データレジスタ内に不良ビットが検知された場合に、不良ブロックとして登録するステップとを具備する。

(もっと読む)

半導体集積回路及びメモリ検査方法

【課題】メモリを初期化するための初期化専用回路を設けることなくメモリを初期化することができ、メモリ中の機密データを完全に消去した後にのみ外部からメモリにアクセス可能な半導体集積回路を提供すること。

【解決手段】半導体集積回路は、機密データを格納するメモリと、メモリBISTを実行するメモリBIST回路と、外部端子を介したメモリアイソレーションテスト用の経路とメモリBIST回路からの経路を切り替える第1のセレクタと、第1のセレクタからの出力の経路と通常回路からの経路を切り替え、出力がメモリに接続される第2のセレクタと、メモリからの出力の経路と擬似信号が入力される経路を切り替え、メモリBIST回路から出力される検査完了信号を選択信号とする第3のセレクタとを備える。この半導体集積回路では、メモリBISTの実行によりメモリが初期化された後、メモリアイソレーションテスト用の経路を介して外部端子からメモリにアクセスされる。

(もっと読む)

半導体集積回路およびその検査方法

【課題】機密データを格納するメモリに対して、メモリに格納されるデータの機密性を確保しつつ、メモリ不良時の解析を容易にする半導体集積回路およびその検査方法を提供する。

【解決手段】機密データを格納するメモリ100と、メモリのWrite/Read動作させる制御回路104と、メモリからの出力データを圧縮するデータ圧縮回路108と、データ圧縮回路から出力される信号を外部モニターできる外部端子110と、メモリからの出力データと正常時に出力されるデータとの比較を行う期待値比較回路109と、期待値比較回路から出力される比較結果の信号を外部モニターできる外部端子111と、メモリからの出力データをテストパスから取り込むことができるテスト回路101bとで構成される。

(もっと読む)

時間測定のための電荷保持回路

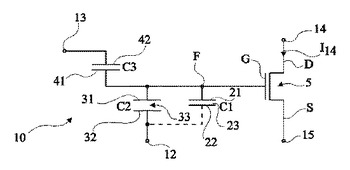

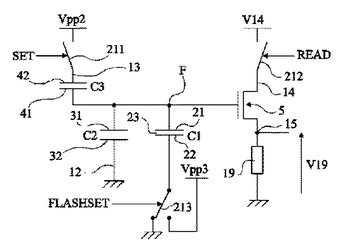

【解決手段】本発明は、時間測定のための電荷保持回路に関し、電荷保持回路は、その第1電極(21)がフローティングノード(F) に接続された少なくとも1つの第1容量性素子(C1)と、その第1電極(31)が前記フローティングノード(F) に接続された少なくとも1つの第2容量性素子(C2)と、前記フローティングノードに接続され、絶縁された制御ターミナルを有する少なくとも1つの第1トランジスタ(5) とを備え、第1容量性素子は誘電体スペーサ(23)を通したリークを有し、第2容量性素子は第1容量性素子のキャパシタンスより大きいキャパシタンスを有する。  (もっと読む)

(もっと読む)

時間測定のための電荷保持回路のプログラミング

【解決手段】本発明は、その誘電体がリークを有する少なくとも1つの第1容量性素子(C1)と、その誘電体が第1容量性素子のキャパシタンスより大きいキャパシタンスを有する少なくとも1つの第2容量性素子(C2)とを備えた時間測定のための電荷保持電子回路であり、前記2つの素子は、残留電荷を測定するために、素子(5) に接続可能なフローティングノード(F) を構成する共通電極を有する前記電荷保持電子回路を制御する方法に関し、電荷保持期間が、第1容量性素子を介した充電又は放電によりプログラミング又は初期化される。  (もっと読む)

(もっと読む)

半導体集積回路及び半導体集積回路の検査方法

【課題】不揮発デバイスを内蔵した半導体集積回路について、不揮発デバイスに実装したデータの機密性を保ちつつテストを行い、エラーがあった場合にエラー位置を特定することを可能とする。

【解決手段】チェック演算回路25は、不揮発デバイス10から読み出された機密情報データに対し、機密CRCデータ生成のための演算に相当する演算を実行する。比較回路26は、チェック演算回路25の演算結果と不揮発デバイス10から読み出された機密CRCデータとの比較を行う。比較結果が不一致でありエラーが検出された場合、暗号処理回路42は、機密情報データと機密CRCデータを秘密鍵レジスタ41に格納された秘密鍵を用いて暗号化し、半導体集積回路外部に出力する。

(もっと読む)

半導体集積回路、半導体集積回路の検査方法、半導体集積回路の検査プログラム

【課題】 暗号用の鍵や個人情報などの秘匿データを内部に持つ半導体集積回路の検査において、高い秘匿性を維持しながらその検査を容易に行える半導体集積回路を提供する。

【解決手段】 秘匿データが格納された第1のROM102と、該第1のROM102と同じ内容のデータが格納された第2のROM103と、前記第1,第2のROM102,103にアクセスするためのアドレスを発生させるアドレス発生回器101と、第1,第2のROM102,103それぞれから読み出された第1,第2の秘匿データS103,S104を比較し、一致・不一致信号S105を、第1の外部端子105を介して当該半導体集積回路100外部に出力する比較回路104と、を備える。

(もっと読む)

半導体メモリおよび半導体メモリのテスト方法

【課題】セキュリティ回路を備える半導体メモリに対して実行する全体機能テストのテストコストを低減させることを課題とする。

【解決手段】メモリ専用テスタ30のバッファには、入力パターンデータIPと出力期待値データEPとが格納されている。読み出された入力パターンデータIPに含まれるアドレスは、半導体メモリ10に転送され、セキュリティ回路11においてデスクランブル処理される。デスクランブル処理されたアドレスは、アドレス変換回路12においてメモリコア13のチェックパターンCPが格納された領域を指定するアドレスに変換される。メモリコア13から出力されたデータ(チェックパターンCP)は、セキュリティ回路11でスクランブル処理され、メモリ専用テスタ30に転送される。メモリ専用テスタ30では、期待値データEP1と読み出されたデータとの間で比較処理が行われる。

(もっと読む)

半導体集積回路、および半導体ウェハ

【課題】耐タンパー性を維持したまま不良原因および不良箇所の絞り込みが可能となる半導体集積回路を提供する。

【解決手段】ROM101のワード線単位で確定される領域106の複数に解析用のデータを予め用意しておき、ROMテスト用BIST回路102に、ROM101の不良解析時にROM101から解析用のデータを出力させて解析用の期待値データと比較し、不一致のとき、フェイル結果(不一致の情報)に加えてROMの不良解析に必要な不一致となったデータビットの行アドレス・列アドレスの情報と不一致のデータビット情報(“1”or“0”)を出力する機能を備えさせる。

(もっと読む)

1 - 10 / 10

[ Back to top ]