Fターム[5L106EE02]の内容

半導体メモリの信頼性技術 (9,959) | 障害・試験箇所 (1,040) | 行ライン、列ライン (255)

Fターム[5L106EE02]に分類される特許

1 - 20 / 255

メモリシステム及びそれのブロック複写方法

半導体記憶装置

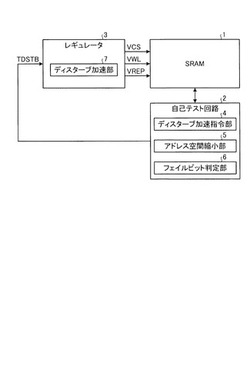

【課題】メモリセルの各トランジスタの特性のランダムばらつきについてのテストを効率化する。

【解決手段】メモリセルMCの動作をテストする自己テスト回路2と、自己テスト回路2からの加速指令に基づいて、メモリセルMCのディスターブが加速するようにワード線WL1〜WLnの電圧VWLまたはメモリセルMCのセル電源電圧VCSを設定するレギュレータ3とを備える。

(もっと読む)

データ生成装置

【課題】簡易な構成で、不良カラムを置き換えたデータを生成可能なデータ生成装置を提供する。

【解決手段】第1記憶部50と第2記憶部36と入力部と出力部65とを含む。第2記憶部は、所定数よりも多い数の記憶領域が直列に接続される。入力部は、ホスト装置から送られるデータを所定数ずつ第2記憶部へ入力する。シフト数決定部66は、欠陥のあるデータ線の数に応じた値を示すシフト数を決定する。出力部は、セクタの識別情報に対応する欠陥情報に基づいて、先頭の記憶領域よりもシフト数だけ後の記憶領域から順番に、当該記憶領域に格納されたデータを、当該セクタ内の欠陥の無いデータ線へ供給するデータとして出力する一方、データとは別の所定情報を、当該セクタ内の欠陥のあるデータ線へ供給するデータとして出力することで、当該セクタに供給される書き込みデータを出力する。

(もっと読む)

半導体記憶装置

【課題】メモリセルのサブスレッショルド・リーク電流の影響によって不良となるデバイスを選別検査で確実にリジェクトする。

【解決手段】行列状に配置された複数のメモリセルMEMと、メモリセルの行に対応して設けられた複数のワード線WL0〜WL4と、メモリセルの列に対応して設けられた複数のビット線対BT0、BB0及びBT1、BB1と、前記複数のワード線のうち、検査対象の注目メモリセル以外の非注目メモリセルが接続された非注目ワード線をフローティングとするスイッチMN1と、前記非注目ワード線がフローティングのときに、当該非注目ワード線を昇圧するポンピング回路POC0とを備える。

(もっと読む)

半導体記憶装置及びその試験方法

【課題】ローデコーダ側に配置される転送トランジスタの特性評価を実施する。

【解決手段】一つの実施形態によれば、半導体記憶装置は、切り替え部、第一の転送トランジスタ、第一のトランジスタ、及び第二のトランジスタが設けられる。切り替え部が第一の状態のときに第一及び第二のトランジスタがオフし、第一の転送トランジスタがオンし、切り替え部が第二の状態のとき第一及び第二のトランジスタがオンする。

(もっと読む)

半導体記憶装置

【課題】全メモリセルのセル電流をテスタを使用して電流測定する場合、全ビット分のセル電流測定に多大な時間を要し、評価効率の低下を招いていた。

【解決手段】電圧端子VDDから抵抗素子R1を介してメモリセルに電流を流し、前記抵抗素子R1での電圧降下値を測定するためのスイッチX2,X3と、前記抵抗素子R1に電圧を印加し、その際に流れる電流値を測定するためのスイッチX1とを設ける。

(もっと読む)

半導体記憶装置及びそのテスト方法

【課題】サブワード線駆動回路を正確に不良検出する技術を提供する。

【解決手段】サブワード選択線を介して供給されるサブワード選択信号を受けるサブワード線駆動回路のテスト方法において、改良されたFXT出力回路とFXB出力回路により、Hi−Z信号とHi信号をサブワード線駆動回路に供給する技術を含む。

(もっと読む)

DRAMをスタックする方法及び装置

【課題】スタックドメモリチップをシグナルインテグリティ等の問題を排除するように構成する。

【解決手段】第1の速度でアクセス可能な複数のセルから構成されるメモリコアを備え、垂直方向にスタックされた複数のDRAM集積回路と、第1の速度よりも大きい速度で、DRAM集積回路とメモリバスとの間でインタフェースを設けるインタフェース集積回路と、メモリスペアリングとを備え、スタックされたDRAM集積回路が(p+q)個のDRAM集積回路を備え、p個のDRAM集積回路が、メモリ集積回路の作業プールとして用いられる複数のDRAM集積回路を備え、q個のDRAM集積回路が、メモリ集積回路のスペアプールとして用いられる複数のDRAM集積回路を備える。

(もっと読む)

半導体装置

【課題】データ書き替えの繰り返しによってメモリセルの閾値電圧が下がりくくなることを防止する。

【解決手段】半導体装置1の各メモリセルMCは、共通の浮遊ゲートFGを有する第1のトランジスタ(読出用)TRAと第2のトランジスタ(書込用)とを含む。制御回路11は、一方のトランジスタに通電したときにメモリセルに流れる電流と、両方のトランジスタに通電したときにメモリセルに流れる電流とを比較することによって、第1および第2のトランジスタにそれぞれ接続されるサブビット線SBL_R,SBL_P間のショートを検出する。

(もっと読む)

半導体装置

【課題】テスト動作時の消費電力を削減できる半導体装置を提供する。

【解決手段】半導体装置は、外部クロック信号を受け取る第1の端子と、第1の端子に接続され、外部クロック信号に応じて内部クロック信号を発生するクロック発生回路と、複数のワード線及び複数のビット線と、複数のビット線にそれぞれ接続された複数の増幅回路と、テスト動作時に、第1の期間の間、複数のワード線のうちの1又は複数のワード線を内部クロック信号に応じて選択状態と非選択状態とを繰り返すように制御し、かつ、第1の期間の間、複数の増幅回路を活性状態に維持し、通常動作時には、複数のワード線のうち1又は複数のワード線の選択状態と非選択状態との切り換えに応じて複数の増幅回路の活性状態と非活性状態とを切り換えるように制御する制御部と、を備える。

(もっと読む)

メモリシステム

【課題】

実施形態は、信頼性を向上可能なメモリシステムを提供する。

【解決手段】

本実施形態のメモリシステムによれば、複数のワード線と、複数のビット線と、制御ゲートに前記ワード線が接続され、ドレイン端に前記ビット線が接続されたメモリセルと、複数の前記メモリセルを含むページ、複数の前記ページを含むブロックを有するメモリセルアレイと、前記ページごとに不良の前記ビットの個数が第1閾値以下である良ブロックに関するデータが保持された記憶領域とを備え、前記第1閾値は、不良ブロックか否かの判定に用いる第2閾値よりも小さいことを特徴とする。

(もっと読む)

半導体装置及びその制御方法

【課題】階層化されたビット線構成のストレス印加テスト時に各ローカルビット線に異なるプリチャージ電圧を供給するための面積増加を抑制し得る半導体装置を提供する。

【解決手段】階層化メモリセルアレイは、グローバルビット線GBL、ローカルビット線LBL、グローバルビット線用のプリチャージ回路Q10、Q11、ローカルビット線用のプリチャージ回路Q20、階層スイッチQ30を備えている。テスト動作時には、高電位と低電位に設定したプリチャージ電圧VBLP0、VBLP1をプリチャージ回路Q10、Q11を介して各グローバルビット線GBLに印加し、かつ各ローカルビット線LBLにプリチャージ電圧VBLPLを印加せず、各階層スイッチQ30を導通させることで1対のローカルビット線LBLに異なる電位の電圧ストレスが印加される。サブアレイSARY毎にプリチャージ電圧VBLPLを2系統に分離するよりも少ない面積で実現できる。

(もっと読む)

試験装置

【課題】装置構成を小さくする。

【解決手段】フェイルデータ及びアドレスデータをバッファリングする第1バッファ部および第2バッファ部と、第1バッファ部にバッファリングされたフェイルデータを、内部メモリにおける当該フェイルデータに対応するアドレスデータに示されたアドレスにRMW処理により書き込むアドレスフェイルメモリ部と、試験部から出力されたフェイルデータ及びアドレスデータを第1バッファ部に供給している状態において、第1バッファ部の空き容量が予め定められた第1閾値以下となった場合に、試験部から出力されたフェイルデータ及びアドレスデータを第1バッファ部に代えて第2バッファ部に供給する制御部とを備える試験装置を提供する。

(もっと読む)

NAND型フラッシュメモリ

【課題】ROMフューズブロックの領域の増加を抑制しつつ、試験中に新たに発生したバッドブロックの情報をより多く記憶することが可能なNAND型フラッシュメモリを提供する。

【解決手段】NAND型フラッシュメモリは、電源投入時において、第1の判定信号が入力され、第1の判定信号の論理をシフトさせながら記憶し、その後、テストモードにおいて、第2の判定信号が入力され、第2の判定信号のバッドブロックの判定に対応する論理のみがアドレスが対応する通常ブロックの論理に上書きされ、且つ、アドレス指定に連動して、記憶している論理が割り当てられたバッドブロックフラグ信号を順次出力するシフトレジスタ回路を備える。

(もっと読む)

不揮発性半導体記憶装置及びそのベリファイ方法

【課題】フューズを用いずにベリファイ読み出しの判定をワイアードオア構成により行うことを可能とし、フューズを設けない分、チップサイズを従来に比較して低減した不揮発性半導体記憶装置を提供する。

【解決手段】本発明の不揮発性半導体記憶装置は、複数のビット線及び複数のワード線各々が交差し、交差した部分に不揮発性のメモリセルが配置されたメモリセルアレイと、メモリセルアレイの欠陥ビット線と置換する冗長ビット線を備える不良置換回路と、ビット線毎に設けられ、ワード線で選択されたメモリセルに書き込むまたは読み出したデータを記憶するラッチを含むページバッファと、ベリファイ処理でビット線から読み出し、ページバッファのラッチに書き込まれたデータを、複数のビット線単位で一括判定する一括判定回路と、欠陥ビット線に対応するページバッファにおけるラッチに疑似データを書き込む疑似データ書込回路とを有する。

(もっと読む)

半導体記憶装置

【課題】メモリセルアレイの占有面積を低減すると共に、使用する電源の容量および占有面積を低減することができる半導体記憶装置の提供を図る。

【解決手段】オープンビット線方式のコアアーキテクチャを有する半導体記憶装置であって、複数のアレイ領域BK0〜BK8,BK0’を有し、前記各アレイ領域は、当該アレイ領域の両端のエッジ部分に配置され、冗長ワード線WLrdのみを有する2つの冗長アレイブロックBK0,BK0’と、前記2つの冗長アレイブロック間でそれぞれセンスアンプSAを介して交互に配置され、リアルワード線WLrlのみを有する複数のリアルアレイブロックBK1〜BK8と、任意の第1アレイ領域で前記リアルワード線を前記冗長ワード線に置き換えるワード線の冗長処理を行うとき、当該第1アレイ領域の電源容量を増大する電源容量制御手段と、を有する。

(もっと読む)

半導体装置

【課題】ストレステストにおいて同時に立ち上げるワード線の本数を増やす。

【解決手段】複数のセンスアンプ列32によって複数のメモリセルマットMATに分割され、其々が複数のワード線WLを備えるメモリセルアレイ30と、複数のメモリセルマットMATの内、選択された互いに隣接しない複数のメモリセルマットMATに其々含まれる複数のワード線WLを同時に立ち上げるテスト制御を行うテスト回路25とを備える。本発明によれば、複数のワード線WLが立ち上がるメモリセルマットMATを分散させていることから、一つのメモリセルマット内において多数のワード線を立ち上げる場合に比べて、ワード線を駆動するためのドライバ回路や、ドライバ回路に動作電圧を供給する電源回路への負荷が軽減する。その結果、より多数のワード線を同時に立ち上げることが可能となる。

(もっと読む)

半導体装置及びその制御方法

【課題】様々な導通状態にある複数の電気ヒューズを有する半導体装置において、複数の電気ヒューズによりプログラミングされた結果を誤判定なく読み出すことのできる半導体装置及び半導体装置の制御方法を提供する。

【解決手段】其々がプログラム状態又は非プログラム状態である複数のヒューズ素子と、複数のヒューズ素子のプログラム状態又は非プログラム状態に対応する判定結果信号FLDa,FLDbを其々出力する複数のヒューズ判定回路92a,92bと、第1のタイミング信号LOAD_ENDを共通に受け、第1のタイミング信号LOAD_ENDに同期して複数の判定結果信号FLDa,FLDbを其々ラッチ及び出力する複数のラッチ回路93a,93bとを備える。

(もっと読む)

ウェハテスト装置、ウェハテスト方法およびプログラム

【課題】ウェハテストのテスト時間を増加させることなく、検出された不良セルがいずれの不良パターンで不良となったのかを検知できるようにすること。

【解決手段】ウェハテスト装置は、第1および第2のテストプログラムを保持する記憶部と、第1のテストプログラムを用いてロット内の複数のウェハのうちの一部のウェハに対するテストを行なうとともに、第2のテストプログラムを用いてロット内の複数のウェハのうちの残部のウェハに対するテストを行なう演算部とを備え、第1のテストプログラムは、ウェハに対して複数の動作テストを実行し、各動作テストが終了するごとにウェハに含まれる不良メモリセルの累積情報を装置の外部に出力し、第2のテストプログラムは、ウェハに対して複数の動作テストを実行し、すべて動作テストが終了した後にウェハに含まれる不良メモリセルの累積情報を装置の外部に出力する。

(もっと読む)

半導体記憶装置

【課題】2個の隣接する列ブロックのいずれにも欠陥がある場合でも、これらの列ブロックの救済が可能な半導体記憶装置を提供する。

【解決手段】データ線シフト回路58は、偶数番目の正規ブロックに欠陥がある場合に、偶数番目の正規ブロックおよび偶数番目のスペアブロックを対象としたシフトリダンダンシ方式によって、偶数番目の内部正規データ線NIOXおよび偶数番目の内部スペアデータ線SIOXと偶数番目の外部データ線EIOXとの接続を行ない、奇数番目の正規ブロックに欠陥がある場合に、奇数番目の正規ブロックおよび奇数番目のスペアブロックを対象としたシフトリダンダンシ方式によって、奇数番目の内部正規データ線NIOXおよび奇数番目の内部スペアデータ線SIOXと奇数番目の外部データ線EIOXとの接続を行なう。

(もっと読む)

1 - 20 / 255

[ Back to top ]