国際特許分類[G01R31/319]の内容

物理学 (1,541,580) | 測定;試験 (294,940) | 電気的変量の測定;磁気的変量の測定 (31,836) | 電気的性質を試験するための装置;電気的故障の位置を示すための装置;試験対象に特徴のある電気的試験用の装置で,他に分類されないもの (15,110) | 電子回路の試験,例.シグナルトレーサーによるもの (5,767) | デジタル回路の試験 (638) | 機能試験 (585) | テスターハードウエア,すなわち,出力処理回路 (178)

国際特許分類[G01R31/319]の下位に属する分類

実際のレスポンスと既知の正確なレスポンスとの比較によるもの

国際特許分類[G01R31/319]に分類される特許

1 - 10 / 178

試験装置および試験方法

【課題】正確なタイミングでサンプリングしたデータ値を期待値と比較する。

【解決手段】データ信号とデータ信号をサンプルするタイミングを示すクロック信号とを出力する被試験デバイスを試験する試験装置であって、データ信号をバッファリングするバッファ部と、当該試験装置の試験周期毎に、制御信号およびデータ信号の期待値を発生するパターン発生部と、試験周期毎に、制御信号がバッファ部からのデータの読出しを指示することを条件として、バッファ部からデータ信号を読み出す読出制御部と、読出制御部により読み出されたデータ信号とパターン発生部から発生された期待値とを比較する判定部とを備える試験装置を提供する。

(もっと読む)

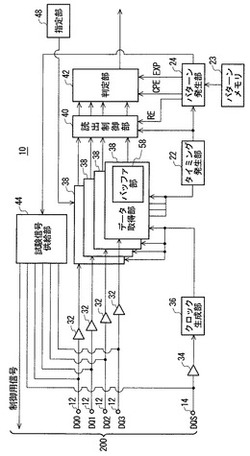

試験装置

【課題】高速多値信号を試験可能な試験装置を提供する。

【解決手段】パターン発生器PGは、I/O端子PIOに入力される被試験信号S1と比較すべきしきい値電圧Vthを指定する制御データS11を発生するとともに、被試験信号S1としきい値電圧Vthの比較結果の期待値を示す期待値データEXP2を発生する。しきい値電圧発生器10は、制御データS11に応じた電圧レベルを有するしきい値電圧Vthを、第1タイミング信号St1が指定する設定タイミングtVごとに生成する。レベルコンパレータCpは、被試験信号S1の電圧レベルをそれと対応するしきい値電圧Vthと比較する。タイミングコンパレータTCは、レベルコンパレータCpの出力S3を、第2タイミング信号St2が指定するストローブタイミングでラッチし、比較信号S4を生成する。タイミング調節部50は第1タイミング信号St1の位相を調節する。

(もっと読む)

試験装置および試験方法

【課題】精度良く被試験デバイスを試験する。

【解決手段】データ信号とクロック信号とを授受する被試験デバイスを試験する試験装置であって、被試験デバイスにデータ信号およびクロック信号を試験信号として供給する試験信号供給部と、被試験デバイスが出力するデータ信号を、被試験デバイスが出力するクロック信号に応じたタイミングで取得するデータ取得部と、データ取得部が取得したデータ信号を期待値と比較した比較結果に基づいて被試験デバイスの良否を判定する判定部と、調整時において、データ信号を取得するタイミングを生成するためのクロック信号の遅延量を調整する調整部とを備える試験装置を提供する。

(もっと読む)

試験装置および試験方法

【課題】被試験デバイスから出力されるクロック信号を取得して試験する。

【解決手段】被試験デバイスが出力するデータ信号を被試験デバイスが出力するクロック信号に応じたサンプリングクロックに応じたタイミングまたは当該試験装置の試験周期に応じたタイミング信号のタイミングで取得するデータ取得部と、データ取得部が取得したデータ信号を期待値と比較した比較結果に基づいて被試験デバイスの良否を判定する判定部と、データ取得部がサンプリングクロックに応じたタイミングまたはタイミング信号に応じたタイミングの何れによりデータ信号を取得するかを指定する指定部と、を備える試験装置を提供する。

(もっと読む)

試験装置および試験方法

【課題】精度良く試験をする。

【解決手段】データ信号とデータ信号をサンプルするタイミングを示すクロック信号とを出力する被試験デバイスを試験する試験装置であって、被試験デバイスが出力するデータ信号を、被試験デバイスが出力するクロック信号に応じたタイミングで取得するデータ取得部と、被試験デバイスがクロック信号を出力しない期間において、データ取得部によるデータ取得をマスクするマスク部と、データ取得部が取得したデータ信号を期待値と比較した結果に基づいて、被試験デバイスの良否を判定する判定部と、を備える試験装置を提供する。

(もっと読む)

試験装置および試験方法

【課題】確実にデータを取り込んで試験する。

【解決手段】データ信号とデータ信号をサンプルするタイミングを示すクロック信号とを出力する被試験デバイスを試験する試験装置であって、被試験デバイスが出力するデータ信号をクロック信号に応じたタイミングで取得する取得部と、複数のエントリを有し、クロック信号に応じたタイミングにおいて取得部により取得されたデータ信号を順次各エントリにバッファリングし、当該試験装置の試験周期に応じて発生されるタイミング信号のタイミングで各エントリにバッファリングしたデータ信号を出力するバッファ部と、バッファ部から出力されたデータ信号を期待値と比較する判定部とを備える試験装置を提供する。

(もっと読む)

基板検査装置および基板検査方法

【課題】基板に形成された凹部の深度を、非破壊、非接触で検査できるとともに、高速に検査できるようにする技術を提供する。

【解決手段】基板検査装置100は、ポンプ光の照射に応じて、基板Wに向けてテラヘルツ波を照射する照射部12と、プローブ光の照射に応じて、基板Wを透過したテラヘルツ波の電場強度を検出する検出部13と、テラヘルツ波が検出部13に到達する時間と、検出部13における検出タイミングを遅延させる遅延部14とを備える。また、基板検査装置100は、基板Wの第1領域を透過した第1テラヘルツ波の時間波形を構築する時間波形構築部21と、基板Wの第2領域を透過した第2テラヘルツ波について、特定の検出タイミングで検出される電場強度と、前記時間波形とを比較することにより、第1テラヘルツ波と第2テラヘルツ波の位相差を取得する位相差取得部24とを備える。

(もっと読む)

プリント基板劣化検査装置および劣化検査方法

【課題】プリント基板を破壊することなく、故障発生前にプリント基板またはプリント基板上の回路(検査部位)の修理もしくは交換を容易にできる劣化検査装置を提供する。

【解決手段】プリント基板劣化検査装置は、パルス波を出力するパルス発生器51と、プローブ32と、オシロスコープ53と、コンピュータ60とを備える。プローブ32は、検査部位と接続されたプリント基板上の配線パターンにパルス波を印加するために用いられる。オシロスコープ53は、パルス波がプリント基板から反射された反射波を、プローブ32を介して測定する。コンピュータ60は、プリント基板または検査部位に対して測定された反射波と比較のための参照用波形に基づいて、プリント基板あるいは検査部位の劣化を判定する。

(もっと読む)

半導体回路の検査装置

【課題】期待値パターンを用いることなく、不良となる半導体回路を特定することのできる検査を短時間に低コストで行なう。

【解決手段】半導体回路に所定のテストパターンを入力することにより出力される信号に基づき前記半導体回路の良否を判断する半導体回路の検査装置において、3以上の前記半導体回路から出力された信号が入力されており、3以上の前記半導体回路から出力された信号のうち多数となる信号を出力する多数決回路と、前記多数決回路からの出力信号と、前記半導体回路からの出力信号のうちいずれかが入力している第1の排他的論理和回路と、を有することを特徴とする半導体回路の検査装置により上記課題を解決する。

(もっと読む)

半導体試験装置

【課題】 正極出力と負極出力との差分値に基づく良否判定にかかる時間を短縮して、被試験デバイスの階調テストに要する時間を短縮する半導体試験装置を提供する。

【解決手段】 本発明の代表的な構成は、FPDドライバ102の階調テストを行う半導体試験装置100において、FPDドライバ102のピンから出力される正極出力または負極出力をA/D変換するA/D変換器112a〜112nと、A/D変換された正極出力または負極出力の一方を記憶しておくメモリ118と、メモリ118に記憶された正極出力または負極出力の一方を出力したものと同じピンについて、A/D変換された負極出力または正極出力の他方の入力を受けて、正極出力と負極出力との差分値を逐次演算する差分演算回路114と、を有することを特徴とする。

(もっと読む)

1 - 10 / 178

[ Back to top ]