国際特許分類[G06F12/12]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | メモリ・システムまたはアーキテクチャ内でのアクセシング,アドレシングまたはアロケーティング (20,382) | アドレシングまたはアロケーション;リロケーション (4,708) | 階層構造のメモリ・システム,例.仮想メモリ・システム,におけるもの (2,277) | 置換制御 (259)

国際特許分類[G06F12/12]に分類される特許

1 - 10 / 259

電子計算機、メモリ管理方法、およびメモリ管理プログラム

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

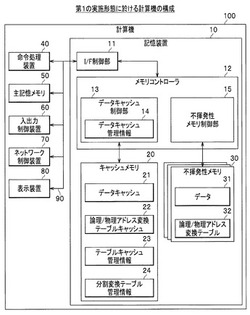

記憶装置および計算機

【課題】不揮発性メモリからキャッシュメモリへの書込回数を削減する。

【解決手段】記憶装置10は、不揮発性メモリ30とキャッシュメモリ20とメモリコントローラ12とを有する。不揮発性メモリ30は、分割データと格納場所を管理する論理/物理アドレス変換テーブル32を記録している。キャッシュメモリ20は、データキャッシュ21と、論理/物理アドレス変換テーブル32の一部を保持する論理/物理アドレス変換テーブルキャッシュ22を記録している。メモリコントローラ12は、外部からデータの読み出し要求を受けたとき、データキャッシュ21上に空きエントリが無かったならば、データキャッシュ21上の分割データのうち、論理/物理アドレス変換テーブル32のエントリが、論理/物理アドレス変換テーブルキャッシュ22に有るものを優先的に不揮発性メモリ30に退避して空きエントリを作成し、データを読み出す。

(もっと読む)

情報処理装置

【課題】ネットワーク透過な単一レベル記憶を実現すること。

【解決手段】本発明の一つの実施形態によれば、情報処理装置は、第1メモリと、第2メモリと、仮想アドレス空間の少なくとも一部の仮想アドレスと前記第1メモリの物理アドレスとの対応関係を管理する変換情報を参照して、前記第1メモリにアクセスする制御部と、を備える。前記仮想アドレス空間には、他の情報処理装置に格納されたデータも割り当てられる。前記制御部は、アクセス対象データが前記他の情報処理装置に格納され手いる状態でページフォールトが発生した場合、前記他の情報処理装置に格納された前記アクセス対象データを前記第1メモリに格納するとともに、前記アクセス対象データに対応する仮想アドレスと前記第1メモリの物理アドレスの対応関係を前記変換情報に登録する。

(もっと読む)

アドレス変換装置、アドレス変換装置の制御方法及び演算処理装置

【課題】エントリのヒット率の低下を抑制できるようにする。

【解決手段】仮想アドレスと物理アドレスとの対応関係を示すアドレス情報がそれぞれ記憶される複数のCAM回路を有するCAM部と、新たなアドレス情報を記憶させる場合に書込みポインタが示しているCAM回路にアドレス情報の書込みを指示する書込み制御部とを有するマイクロTLBにおいて、書込みポインタが示しているCAM回路に記憶されているアドレス情報が、アドレス変換に使用されたことが示されている場合には書込みポインタをインクリメントするようにして、アドレス情報の使用が示されたCAM回路に新たなアドレス情報が書込まれることを回避して最近使用されているアドレス情報を保持し、ヒット率の低下を抑制する。

(もっと読む)

演算処理装置及び演算処理装置の制御方法

【課題】使用頻度の高い論理アドレス空間が頻繁に入れ替わることを防止する演算処理装置を提供することを課題とする。

【解決手段】アドレス変換対を記憶するバッファ領域を有する記憶装置に接続される演算処理装置において、複数の論理アドレスレジスタのうち使用履歴が最も古い論理アドレスレジスタの番号を保持するLRUレジスタと、記憶装置に対するアクセス要求に含まれる論理アドレスが、下限論理アドレスレジスタが保持する下限論理アドレスから上限論理アドレスレジスタが保持する上限論理アドレスまでの論理アドレス空間の範囲に入っていない場合、LRUレジスタが保持する論理アドレスレジスタの番号を読み出す読み出し部(S502)と、読み出された番号の論理アドレスレジスタを無効にし、アクセス要求に含まれる論理アドレスに対応する論理アドレス空間を、無効にした論理アドレスレジスタに設定する設定部(S410)を有する。

(もっと読む)

マルチレベルのキャッシュ階層におけるキャストアウトを低減するための装置および方法

【課題】下位レベルキャッシュから置換されたキャッシュラインの上位レベルキャッシュへの割り当てを低減する方法を提供する。

【解決手段】置換ラインがすでに上位レベルに割り当てられと決定されたとき、置換されたキャッシュラインの割り当ては、次のレベルキャッシュにおいて防がれ、これにより、キャストアウトが低減する。そのような目的に、ラインは、下位レベルキャッシュ204において置換されるように選択される。上位レベルキャッシュ208において選択されたラインが存在するか示す選択されたラインに関連する情報が識別される。上位レベルキャッシュにおける選択されたラインの割り当ては、識別された情報に基づいて防がれる。選択されたラインの割り当てを防ぐことは、割り当てに関連するであろう電力を蓄える。

(もっと読む)

記憶制御システムおよび方法、置換方式および方法

【課題】キャッシュ置換方法に関し、無駄なプリチャージを削減しメモリの消費電力を削減する。

【解決手段】DRAM100内のロウバッファ102は、メモリアレイ101から所定のデータ長を単位とするいずれかのデータを読み出して格納する。LLC206は、ロウバッファ102に記憶されたデータの一部をキャッシュデータとして抽出して記憶するキャッシュメモリである。MAC601において、LLC206の追い出し制御が実施される場合に、MRQ203のキューイング状態に基づいて近い将来ロウバッファ102にどのDIMMアドレスのデータが記憶されるかを予測する。MACにおいて、LLC上の追い出し対象範囲702のキャッシュデータデータの各物理アドレスをDIMMアドレスに変換する。変換された各アドレスと予測されたデータのアドレスとが一致した場合に、その一致アドレスに対応するキャッシュデータを優先してLLCから追い出す。

(もっと読む)

メモリページ管理

【課題】シーケンシャルアクセスされる一つ以上のデータ構造のために用いられるメモリをページングするための方法、ならびにそれに対応するソフトウエアおよびシステムを提供する。

【解決手段】メモリページの再使用順序を表すデータ構造200を提供するステップ、およびシーケンシャルアクセスされるデータ構造の一つと関係付けられる、メモリページへのアクセス履歴に基づいて、データ構造を維持するステップを含む。その順序におけるメモリページの位置は、メモリページからのシーケンシャルアクセスの移行に依存する。

(もっと読む)

キャッシュメモリの最大レジデンシー交換のための方法およびシステム

【課題】キャッシュメモリの複数のセットウエイのレジデンシーを最大にするようにキャッシュメモリアロケーションを交換する方法を提供する。

【解決手段】ビクティムウエイのファーストイン、ファーストアウト(FIFO)交換リストを形成する。FIFO交換リストの深さは、キャッシュセット内の数にほぼ等しい。タグミスアロケーションを生じた場合にのみビクティムウエイをFIFO交換リスト上に配置する。ビクティムウエイは任意の以前に選択されたビクティムウエイの後でFIFO交換リストのおわりに配置される。ビクティムウエイのイニシャルアロケーションが完了するまで引き止めておくことにより、またはビクティムウエイのイニシャルアロケーションが完了するまで再使用リクエストをリプレイ(replay)することによりビクティムウエイの不完全な先のアロケーションの場合にFIFO交換リスト上のビクティムウエイの使用が防止される。

(もっと読む)

処理パイプラインの制御

【課題】処理パイプライン内の処理バブルの低減が可能なデータ処理装置を提供する。

【解決手段】グラフィクス処理ユニットは、第1パイプライン部分18と第2パイプライン部分20とを有するテクスチャパイプライン6を含む。第1パイプライン部分18内の主題命令は、その主題命令によりメモリからロードされる記述子データが、共有記述子キャッシュ内に貯えられるまで、第1パイプライン部分18内で再循環される。記述子が、共有キャッシュ内に保存されている場合、主題命令は、追加の処理操作が実行される第2パイプライン部分20に渡され、それらの追加の処理操作が完了するまで再循環される。記述子データは、その記述子データを利用するのに必要とされるテクスチャパイプライン6内の係属中の主題命令がなくなるまで、共有記述キャッシュ内に固定される。

(もっと読む)

1 - 10 / 259

[ Back to top ]