国際特許分類[G06F13/28]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | メモリ,入力/出力装置または中央処理ユニットの間の情報または他の信号の相互接続または転送 (29,400) | 相互接続または転送のための接続要求 (2,939) | 入力/出力バスに対するアクセスのためのもの (715) | バーストモード転送を用いるもの,例.ダイレクトメモリアクセス,サイクルスチール (558)

国際特許分類[G06F13/28]の下位に属する分類

優先制御によるもの (7)

国際特許分類[G06F13/28]に分類される特許

1 - 10 / 551

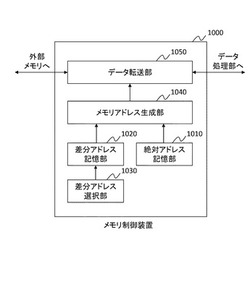

メモリ制御装置、メモリ制御方法、データ処理装置、画像処理システム

【課題】回路規模を抑えつつデータ整列が完了した状態で外部メモリから内部メモリにデータを転送する方法が求められていた。

【解決手段】本発明のメモリ制御装置は、外部メモリから複数の処理機構を備えるデータ処理手段にデータを転送するメモリ制御装置であって、所定のデータ転送期間において共通の基準値となる絶対アドレスを記憶する絶対アドレス記憶手段と、複数の差分アドレスを記憶する差分アドレス記憶手段と、複数の差分アドレスを所定の順序で選択する差分アドレス選択手段と、差分アドレス選択手段が選択した差分アドレスと絶対アドレスとを組み合わせてメモリアドレスを生成するメモリアドレス生成手段と、メモリアドレス生成手段で生成されるメモリアドレスを外部メモリに入力し、メモリアドレスからデータを読み出してデータ処理手段にデータを転送するデータ転送手段と、を具備する。

(もっと読む)

データ転送装置、データ転送方法およびプログラム

【課題】 チェーンリストによるDMA転送において転送データの任意の位置に挿入、削除を行いながら転送すること。

【解決手段】 データ転送装置は、転送元のデータの配置情報を示す第1のリスト、転送先のデータの配置情報を示す第2のリスト、挿入するデータの配置情報を示す第3のリスト、および削除開始の位置を示す削除オフセットアドレスと削除するデータのデータサイズとを有する第4のリストを取得する取得部と、受信した転送要求に従って、取得部により取得された第1のリスト乃至第4のリストから必要なリストを選択して、転送元から転送先に転送するためのデータを生成する制御部と、制御部により生成されたデータを転送先に転送する転送部と、を備える。

(もっと読む)

情報処理装置及び情報処理方法

【課題】シリアルバスを介してデータが転送される場合であっても、メモリを増加することなく、レイテンシの発生を防止することが可能な情報処理部100aを提供する。

【解決手段】前記CPU201からの要求が、前記第一のDMAコントローラ206に前記第二のRAM210のデータを読み取らせて前記第一のRAM209に書き込ませる間接リード要求であるか否かを判定する要求判定手段302と、前記要求が前記間接リード要求である場合に、当該間接リード要求を、前記第二のDMAコントローラ207に前記第二のRAM210のデータを前記第一のRAM209に書き込ませる直接ライト要求に変換する要求変換手段303と、前記直接ライト要求を前記第二のDMAコントローラ207に送信する要求送信手段304とを備える情報処理部100aを提供する。

(もっと読む)

マルチCPUコア・プロセッサ用DMAC付きDRAMアドレス・マッピング回路

【課題】CPUシステム(PC,TabletPC,PDA etc.)において、CPUコアもしくはOSが32bitであると主記憶サイズは4GB以下の3.5GB程度に制約される。 現状4GB(3.5GB)を超えて搭載したメモリーは無駄となる。 また、実行速度改善に効果がある現在のRAMDISKは主記憶を使う為、主記憶サイズの制限は、32bitシステムでの性能向上の足かせとなっている。

【解決手段】DRAMのローカル・アドレスをシステム物理アドレスにマッピングする回路にDMA機能を持たせる事により、主記憶に割り振れなかったDRAM領域をRAMDISKとして経済的に使用し、かつ、それに関わるデータ転送をDRAMのローカルバス上で局所的に行う事で、従来の主記憶を使ったRAMDISKより、実行効率の良いRAMDISKを供給する。

(もっと読む)

情報処理装置及びメモリ管理方法

【課題】 転送装置から転送されてくる画像データを効率的に処理できる情報処理装置およびメモリ管理方法を提供することを目的とする。

【解決手段】 実施形態によれば、情報処理装置は、メモリと、テーブルと、変更手段と、通知手段とを有する。メモリは、複数の画像データを保持する複数のバッファ領域を有する。テーブルは、複数のバッファ領域を画像データが書き込まれる受信バッファと画像データを保持する保持バッファとに割り当てる。変更手段は、前記受信バッファに書き込まれた画像データを保持する場合、前記保持すべき画像データが書き込まれた受信バッファと保持バッファとを入れ替える。通知手段は、変更手段により受信バッファと保持バッファとを入れ替えた場合、変更後の受信バッファを示す情報を画像転送元へ通知する。

(もっと読む)

情報処理装置およびプログラム

【課題】転送データの入出力処理に際してより効果的に低消費電力化を行う。

【解決手段】実施形態の情報処理装置は、記憶部上の領域を示す情報と、領域を示す情報が格納されるエントリの状態を示す状態情報とを含むデスクリプタを作成部が作成し、入出力部による状態情報に従い選択したエントリに示される領域に対するデータの書き込みおよび読み出しのうち少なくとも一方に応じて、更新部が状態情報を更新する。作成部は、デスクリプタを、記憶部に対するデータの書き込みおよび読み出しのうち少なくとも一方が開始される前に予め作成する。

(もっと読む)

印刷装置および印刷装置のデータ転送方法

【課題】転送パラメーターの設定が失敗したとしても、エラーから自動復帰して、印刷データのDMA転送を継続することができる。

【解決手段】統括制御部22は、分割したDMA転送毎の転送パラメーターを、受信部に設定する転送設定部41と、DMA要求信号を受信部11、21に送信する信号送信部42と、信号送信部42を制御する信号制御部43と、を有し、受信部11、21は、DMA要求信号のアサートエッジに起因し、設定した転送パラメーターに基づいて、統括制御部22に対しDMA転送を行うDMA転送部33を有し、信号制御部43は、分割したDMA転送毎に、アサートエッジを生じさせると共に、DMA要求信号がアサート状態を所定時間以上継続している場合、アサートエッジを生じさせる。

(もっと読む)

データ転送制御装置及び方法

【課題】二次元DMACを用いたデータ転送制御装置において、従来技術に比較してデータバスの使用効率を高めることができるデータ転送制御装置及び方法を提供する。

【解決手段】ダイレクトメモリアクセスコントローラを用いたデータ転送制御装置であって、転送先のアドレス、リードもしくはライトを指定するコマンドを発行するコマンド制御部と、データ転送の際に記憶装置制御回路よりタグ情報を受け取ることでどのコマンドに対するデータ転送か判別するために、コマンド発行の際にタグ情報を生成するタグ生成部と、上記タグ情報にアドレスオフセットの情報を含め、データ転送の際に当該データに対応するアドレスオフセットの情報を受けとり、上記記憶装置制御回路から受けとったデータから上記アドレスオフセットの情報に基づいて有効データの選択を行って出力する有効データ選択部とを備える。

(もっと読む)

DMA制御装置

【課題】DMAを行う複数のパイプラインを、簡単な設定により任意に接続できるようにし、またデータ交換の単位も、点・線・面・立体など柔軟に対応でき、さらに時分割制御により見かけ上同時実行可能なDMA装置を提供すること。

【解決手段】複数のDMA設定に対し、設定単位ごとに時分割スケジューリングを行う。自らのDMAの指標と接続するDMAの指標との比較結果を用いた起動制御を行い、さらに処理の順序関係を保証する。

(もっと読む)

画像形成装置

【課題】画像の印刷時にアンダーランをより確実に防止することが可能な画像形成装置を提供する。

【解決手段】第1のDMA制御部17は、転送要求R1の時にFIFO25に一時蓄積されている黒成分データの量を主走査ライン数に換算した情報I1を、転送要求R1と一緒にバス調停部35に送る。第2のDMA制御部19Cは、転送要求R2の時にFIFO31Cに一時蓄積されているシアン成分データの量を主走査ライン数に換算した情報I2を、転送要求R2と一緒にバス調停部35に送る。前記第1のDMA転送要求と前記第2のDMA転送要求とが競合した場合、情報I1で示される主走査ライン数が情報I2で示される主走査ライン数よりも小さければ、第1のDMA制御部17にバス21の使用権が与えら、情報I2で示される主走査ライン数が情報I1で示される主走査ライン数よりも小さければ、第2のDMA制御部19Cにバス21の使用権が与えられる。

(もっと読む)

1 - 10 / 551

[ Back to top ]