国際特許分類[G06F9/315]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | プログラム制御のための装置,例.制御装置 (15,360) | プログラム記憶方式を用いるもの,すなわちプログラムを受取りそして保持するために処理装置の内部記憶装置を用いるもの (15,354) | 機械語命令を実行するための装置,例.命令デコーダ (1,710) | 移動,桁送りまたは回転の演算を制御するもの (20)

国際特許分類[G06F9/315]に分類される特許

1 - 10 / 20

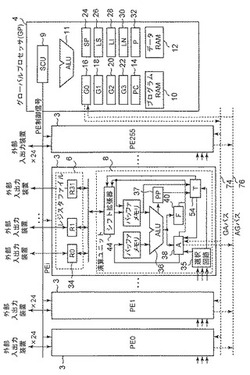

プロセッサ装置及びその演算方法

【課題】複数のPEを備えた並列型SIMDプロセッサにおいて並列性の高い行列転置方法等を提供する。

【解決手段】プロセッサ装置は、各PE方向に行ベクトルデータが配列され、かつ各PE内レジスタ方向に列ベクトルデータがそれぞれ配列された複数個の行列データの数学的転置を行うときに、各PE間のレジスタ参照、格納又は移動を行う単一命令複数データ型の演算命令を用いて、対角位置の要素データ又はベクトルデータの移動をして交換を行うステップを含み、行列に含まれる2のべき乗次の部分行列を対象にして、最小2次の行列(2×2要素)では対角要素データの移動又は交換を行い、上位のべき乗次数の部分行列では対角位置の下位の部分行列の要素データ群をブロックとして一括に移動又は交換し、これらの手順を上位次数から最小次数まで、又は最小次数から上位次数まで順次繰り返して行って複数の行列データを一括して並列同時に転置処理する。

(もっと読む)

ベクトルマスク設定技術

【課題】本発明の課題は、マイクロプロセッサアーキテクチャの命令セットアーキテクチャにおいて使用される効果的なベクトルマスク生成技術を提供することである。

【解決手段】本発明によると、上記課題は、ベクトルマスクを格納するための第1処理を検出する第1ロジックと、前記第1処理より以前のベクトルマスク値を生成するための最新の第2処理を特定する第2ロジックと、前記第2処理が特定される場合、前記第1処理の実行を回避する第3ロジックとから構成されることを特徴とするプロセッサにより解決される。

(もっと読む)

データ選択とデータ整列またはデータ複製とを組み合わせることを含む多段階の多重化操作

データ選択とデータ整列またはデータ複製とを組み合わせることを含む、多段階の多重化操作が開示される。ある具体的な実施形態では、方法は、多段階の多重化操作の第1の段階を実行するステップを含む。第1の段階の間に、第1のデータソースが、第1の複数のデータソースから選択される。第1のデータ整列操作と第1のデータ複製操作のうちの少なくとも1つも、第1の段階の間に選択された第1のデータソースからの第1のデータに対して、実行される。  (もっと読む)

(もっと読む)

データをシャッフルするための方法及び装置

【課題】効果的にデータをシャッフルするための方法及び装置を提供すること。

【解決手段】一実施例の方法は、L個のデータ要素を有する第1オペランドとL個の制御要素を有する第2オペランドとを受け取ることからなる。各制御要素に対して、当該制御要素により指定された第1オペランドデータ要素からのデータは、それのゼロクリアフィールドが設定されていない場合に関連付けされた結果のデータ要素位置にシャッフルされ、それのゼロクリアフィールドが設定されていない場合、関連付けされた結果のデータ要素位置にゼロが配置される。

(もっと読む)

単一命令でシフトおよび排他的論理和演算を行う方法および装置

シフトおよびXOR演算を実行する方法および装置が開示される。一実施形態では、装置は、第1の命令を実行する実行リソースを含む。第1の命令に呼応して、実行リソースは、少なくとも1つの値にシフトおよびXORを行う。 (もっと読む)

キャリーフラグの読み出しを伴わずに実行を完了する回転命令

【課題】命令処理装置の実行部において、並列処理および/または投機的な実行を制限し、時間がかかるキャリーフラグの読み出しを伴うことなく、回転命令を実行できるようにする。

【解決手段】ソースオペランドと回転量とを示す回転命令を受信し(221)、回転命令が示すデスティネーションオペランドに、回転量で回転させたソースオペランドを有する結果を格納する(222)ことにより、キャリーフラグの読み出しを伴わずに回転命令の実行を完了する(223)。

(もっと読む)

情報処理装置および画像信号処理方法

【課題】容易な演算処理でEMIを軽減させることができる情報処理装置および画像信号処理方法を提供する。

【解決手段】GPU114は、データ入れ替え処理部300に入力された画像信号を、例えば表示された画面上の1ドットを1構成画素単位(例えば、4bit、8bit等、またはRGB(カラーモデル)の画素単位等でもよい)として画像信号の記憶メモリに順次、書き込む。データ入れ替え処理部300は、画像信号の記憶メモリに書き込むべき順番で時系列に配置し、GPU114に対して出力する。GPU114は、表示部であるLCD17に画像信号を出力する制御等を行う。

(もっと読む)

演算器及び半導体集積回路装置

【課題】動作速度を向上出来る演算器及び半導体集積回路装置を提供すること。

【解決手段】複数ビットを一つのデータ単位S0〜S3とするSIMD命令を、複数の処理サイクルPS1、PS2により実行する演算器10であって、前記データ単位S0〜S3間でのビットの移動を伴うことなく、それぞれ前記データ単位S0〜S3毎に第1演算を行う複数の第1演算部11−0〜11−3と、前記データ単位S0〜S3間でのビットの移動を伴う第2演算を行う第2演算部12とを具備し、前記第1演算と前記第2演算とにより前記SIMD命令が実行され、且つ前記第1演算と前記第2演算とは、互いに1処理サイクル以上のレイテンシを有して実行される。

(もっと読む)

データの順列演算を実行するための装置および方法

順列演算を実行するための順列回路を有する処理回路と、データを格納するための複数のレジスタを有するレジスタバンクと、プログラム命令に応答して処理回路を制御し、データ処理演算を実行する制御回路と、を含む処理データのための装置が提供される。制御回路は、制御生成命令に応答して、ビットマスクに基づいて制御信号を生成し、入力オペランドに対して順列演算を実行するための順列回路を構成するように構成される。ビットマスクは、第1の順序を有する第1のグループのデータ要素と第2の順序を有する第2のグループのデータ要素とを前記入力オペランド内で特定し、順列演算は、前記第1の順序と前記第2の順序とのうちの一方を保存するが、前記第1の順序と前記第2の順序とのうちの他方を変える。  (もっと読む)

(もっと読む)

ROTATETHENINSERTSELECTEDBITSファシリティ及びそのための命令

【課題】 ROTATE THEN INSERT SELECTED BITSファシリティ及びそのための命令を提供する。

【解決手段】 コンピュータを動作させる方法において、Zビットを有するrotate−then−insert命令が、フェッチ及び実行され、第1レジスタの第1オペランドがある量だけ回転される。Zビットが「0」である場合、ブール演算の結果の選択された部分が第2レジスタの第2オペランドの対応するビットに挿入される。Zビットが「1」である場合、挿入されたビットに加えて、第2オペランドの挿入されたビット以外のビットが0に設定される。

(もっと読む)

1 - 10 / 20

[ Back to top ]