国際特許分類[G11C11/15]の内容

物理学 (1,541,580) | 情報記憶 (112,808) | 静的記憶 (17,688) | 特定の電気的または磁気的記憶素子の使用によって特徴づけられたデジタル記憶装置;そのための記憶素子 (6,432) | 磁気的素子を用いるもの (887) | 薄膜素子を用いるもの (879) | 多層の磁性層を用いるもの (856)

国際特許分類[G11C11/15]に分類される特許

1 - 10 / 856

記憶素子、記憶装置

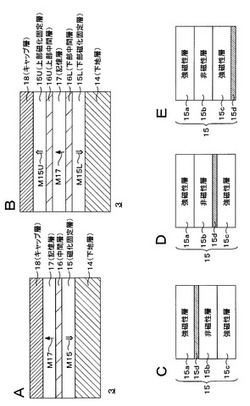

【課題】熱安定性の情報書き込み方向に対する非対称性をすくなくし特性バランスに優れた記憶素子を実現する。

【解決手段】記憶素子は、膜面に垂直な磁化を有し、情報に対応して磁化の向きが変化される記憶層と、上記記憶層に記憶された情報の基準となる膜面に垂直な磁化を有する磁化固定層と、上記記憶層と上記磁化固定層の間に設けられる非磁性体による中間層とを有する層構造を備える。そして上記層構造の積層方向に電流を流すことで記憶層の磁化の向きが変化して、記憶層に対して情報の記録が行われる。この場合に、磁化固定層を少なくとも2層の強磁性層と非磁性層とを有する積層フェリピン構造とし、かつ、いずれかの上記強磁性層に接して反強磁性酸化物層が形成されているようにする。

(もっと読む)

記憶素子、記憶装置

【課題】熱安定性を確保して特性バランスに優れた記憶素子を実現する。

【解決手段】記憶素子は、膜面に垂直な磁化を有し、情報に対応して磁化の向きが変化される記憶層と、上記記憶層に記憶された情報の基準となる膜面に垂直な磁化を有する磁化固定層と、上記記憶層と上記磁化固定層の間に設けられる非磁性体による中間層とを有する層構造を備える。

そして、上記記憶層は非磁性体と酸化物が積層された積層構造層を含み、上記層構造の積層方向に電流を流すことにより、上記記憶層の磁化の向きが変化して、上記記憶層に対して情報の記録が行われる。

(もっと読む)

記憶素子、記憶装置

【課題】熱安定性の情報書き込み方向に対する非対称性をすくなくし特性バランスに優れた記憶素子を実現する。

【解決手段】記憶素子は、膜面に垂直な磁化を有し、情報に対応して磁化の向きが変化される記憶層と、上記記憶層に記憶された情報の基準となる膜面に垂直な磁化を有する磁化固定層と、上記記憶層と上記磁化固定層の間に設けられる非磁性体による中間層とを有する層構造を備える。そして上記層構造の積層方向に電流を流すことで記憶層の磁化の向きが変化して、記憶層に対して情報の記録が行われる。この場合に、磁化固定層を少なくとも2層の強磁性層とCrを含む非磁性層とを有する積層フェリピン構造とする。

(もっと読む)

抵抗変化型不揮発性メモリ

【課題】抵抗変化型不揮発性メモリのメモリセルの面積を縮小し、かつ、消費電力を少なくする。

【解決手段】行選択線をゲート端子に接続したメモリセル選択用トランジスタと抵抗変化型素子を直列に接続した回路のメモリセルの端子をビット線とソース線とに接続した抵抗変化型不揮発性メモリの前記ソース線を前記行選択線に平行に配線し、前記ビット線を前記行選択線に直交させて配線し、前記ソース線に一定値のソース電圧を加えて前記メモリセルへのデータの書き込み及び読出しを行い、前記ビット線に、前記ソース電圧より高い電圧と低い電圧とを切り替えて加えることで異なる値のデータを前記メモリセルへ書き込む。

(もっと読む)

半導体記憶装置およびその駆動方法

【課題】消費電力を低減し、かつ、高速動作を実現することができる不揮発性半導体記憶装置を提供する。

【解決手段】メモリは、不揮発性のセルアレイMCAを備える。パワージェネレータPGは電源電圧を生成する。第1のレシーバRCAは、セルアレイの動作を決定するコマンドおよびアドレスを受け取る。パワーコントローラPCは、セルアレイ、パワージェネレータおよび第1のレシーバのそれぞれの起動状態を制御する。第1のパワーセーブモードでは、セルアレイ、パワージェネレータおよび第1のレシーバを休止状態にする。第2のパワーセーブモードでは、セルアレイ、パワージェネレータを起動状態にし、第1のレシーバを休止状態にする。第3のパワーセーブモードでは、パワージェネレータの少なくとも一部を起動状態にし、セルアレイおよび第1のレシーバを休止状態にする。

(もっと読む)

強磁性トンネル接合素子

【課題】低駆動電流値で電流誘起磁化反転を行うことのできる強磁性トンネル接合素子を提供する。

【解決手段】磁化固定層100と非磁性絶縁層110と磁化自由層120を有する強磁性トンネル接合素子10において、磁化自由層120は非磁性金属層221を挟んで強磁性層220、222を有し、2つの強磁性層220、222の磁化の方向が互いに平行である。2つの強磁性層の磁化の方向を互いに平行にすることにより、スピントランスファートルクが有効に働き、駆動電流を低減できる。

(もっと読む)

不揮発性メモリ

【課題】メモリセルへのデータの書き込みと読出しの信頼性を高くした不揮発性メモリを提供する。

【解決手段】2つのメモリセルを隣接させた基本ユニットを単位にするメモリセルアレイを有し、前記基本ユニットの2つのメモリセルのメモリセル選択用トランジスタのソース端子を共通のソース線に接続し、前記2つのメモリセルを2つのビット線に接続した抵抗変化型メモリであって、前記ソース線の配線パターンと前記ビット線の配線パターンを平行に走行させ、前記ソース線の配線パターンと前記ビット線の配線パターンの一部の領域を上下で重ねあわせて対向させる。

(もっと読む)

半導体記憶装置

【課題】誤書込を抑制することが可能なMRAM装置を提供する。

【解決手段】三角波状のパルス電流Iwをワード線に流してパルス磁場をトンネル磁気抵抗素子の自由層に印加する。また、パルス電流Iwがピークに達した後にピークに達する三角波状のパルス電流Ibをビット線に流してパルス磁場を自由層に印加する。これにより、自由層の磁化ベクトルの歳差運動をその熱揺動よりも大きくして、パルス電流Iwのみで自由層の磁化方向が反転するのを防止できる。また、パルス電流Ibによって自由層の磁化方向を確実に反転させることができる。

(もっと読む)

半導体記憶装置

【課題】共通データバスを共有する複数のローカルメモリユニットが重複してデータを転送すること、あるいは、複数のローカルメモリユニットに対して重複してデータを転送することを抑制した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセルを含む複数のローカルメモリユニットLMU<0>〜LMU<7>を備える。共通データバスDBは、複数のローカルメモリユニットに共有され、複数のローカルメモリユニットからデータを転送し、あるいは、複数のローカルメモリユニットへデータを転送する。タイミングコントローラT/Cはローカルメモリユニットの単位で配置するのではなく、インターリーブ動作を行なう単位(ローカルメモリユニットLMU<0>〜LMU<7>のグループ)に対して1つ配置する。これにより読出しデータまたは書込みデータは、共通データバスDBにおいて衝突しない。

(もっと読む)

半導体記憶装置およびその駆動方法

【課題】書込みまたは読出し時における消費電力を低減させた半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、ビット線対BLP0〜BLP7と、ワード線WL0〜WL3と、各ビット線対の第1のビット線と第2のビット線との間に接続されたメモリセルMCとを備える。スイッチング部CSW1は、ビット線対のうち第1のビット線対グループBLP1、BLP3、BLP5、BLP7または第2のビット線対グループBLP0、BLP2、BLP4、BLP6のいずれかを複数のデータ線LDQ1に選択的に接続する。データ読出し動作またはデータ書込み動作において、スイッチング部は、複数のワード線のうち選択されたワード線が活性化されている1活性化期間中に、第1のビット線対グループを複数のデータ線に接続する第1のスイッチング動作と、第2のビット線対グループを複数のデータ線に接続する第2のスイッチング動作との両方を実行する。

(もっと読む)

1 - 10 / 856

[ Back to top ]