国際特許分類[G11C17/04]の内容

物理学 (1,541,580) | 情報記憶 (112,808) | 静的記憶 (17,688) | 一度だけプログラム可能なリードオンリメモリ;半永久的記憶装置,例.手でリプレースできる情報カード (379) | 容量的素子を用いるもの (6)

国際特許分類[G11C17/04]に分類される特許

1 - 6 / 6

不揮発性半導体記憶装置

【課題】容量素子が占有する回路面積の増大を抑制する。

【解決手段】メモリストリングは、複数の第1導電層、メモリゲート絶縁層、及び半導体層を有する。複数の第1導電層は、半導体基板に対して実質的に垂直方向に所定ピッチをもって配列され、メモリトランジスタのゲートとして機能する。半導体層は、複数の第1導電層と共にメモリゲート絶縁層を一方の側面で挟み、半導体基板に対して実質的に垂直方向に延び、メモリトランジスタのボディとして機能する。第1キャパシタは、複数の第2導電層を有する。複数の第2導電層は、半導体基板に対して実質的に垂直方向に所定ピッチをもって配列され、第1キャパシタの電極として機能する。制御回路は、複数の第1導電層に印加される電圧に応じて、複数の第2導電層の各々に印加する電圧を制御し、これにより第1キャパシタの容量を変化させる。

(もっと読む)

アンチヒューズ回路及び半導体記憶装置

【課題】低電圧で動作する半導体集積回路においても十分動作マージンが確保できるアンチヒューズ回路及びアンチヒューズ回路を備えた半導体記憶装置を提供する。

【解決手段】書き込み時に電位が高いほうから順番に第1乃至第5の電源電圧となる第1乃至第5の電源を使用するアンチヒューズ回路であって、第2乃至第4の電源に接続され、第3の電源電圧と第4の電源電圧との間で変化する第1の論理信号を第2の電源電圧と第4の電源電圧との間で変化する第2の論理信号に変換する第1のレベルシフト回路と、第1、第2及び第4の電源に接続され、第2の論理信号を第1の電源電圧と第4の電源電圧との間で変化する第3の論理信号に変換する第2のレベルシフト回路と、ソースに第1の電源が接続され、ゲートに第3の論理信号が接続されたトランジスタと、一端がトランジスタのドレインに接続され、他端が第5の電源に接続されたアンチヒューズ素子と、を備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】記憶素子として用いられるアンチフューズ素子の絶縁膜の薄膜化に伴う0データの保持特性の悪化を許容し、安価で信頼性が高い不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、読み出し信号READの入力後所定のタイミングでセンスノード11aを初期化する初期化信号EQLを出力すると共に、入力後所定のタイミングでセンスアンプ14を活性化させるための読み出し動作用センスアンプ活性化信号NASEを出力する制御回路21と、通常のデータ読み出しが実行される場合に、読み出し動作用センスアンプ活性化信号NASEをセンスアンプ活性化信号SAEとして出力する一方、アンチフューズ11のゲート絶縁膜を破壊される前のテストの実行が指示された場合に、読み出し信号READの反転信号をセンスアンプ活性化信号SAEとして出力する切り替え回路22とを備える。

(もっと読む)

電気ヒューズ回路及び電子部品

【課題】信頼性の高い電気ヒューズ回路を提供することを課題とする。

【解決手段】電気ヒューズを構成するキャパシタ(101)と、ライト信号に応じて前記キャパシタの端子に電圧を印加することにより、前記キャパシタの絶縁膜を破壊するライト回路(103)と、前記キャパシタ及び前記ライト回路間に直列接続される少なくとも2個の第1及び第2のトランジスタ(112,102)とを有することを特徴とする電気ヒューズ回路が提供される。

(もっと読む)

不揮発性半導体記憶装置

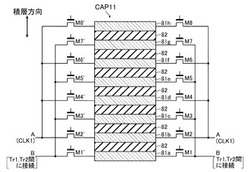

【課題】OTPメモリの多ビット同時書き込みを可能とする。

【解決手段】 ワード線制御回路WSを配置して、各ワード線に共通接続されたセルトランジスタのゲートにクロック信号CLKを印加している。そして、クロック信号CLKがロウレベルの期間はセルトランジスタがオフのため、絶縁破壊されたキャパシタに係るメモリセルも含めて全てのメモリセルに電流が流れない。そのため、最初の書き込みで一旦共通電源電圧VCCの高電圧値が下がり、書き込み可能電圧以下になったとしても、クロック信号CLKがロウレベルの期間で、共通電源電圧VCC及びデータ線DLが書き込み可能電圧まで上昇される。そして、共通電源電圧VCC及びデータ線DLが回復し、十分な電流供給能力を有した後にクロック信号CLKをロウレベルからハイレベルに変化させることで、残りのメモリセルについて書き込みを行う。

(もっと読む)

OTPヒューズ回路

【課題】 未書き込み状態でも読み出し出力を確定させ、使用する回路を動作可能にすると共に、書き込みを2回可能にするOTPヒューズ回路を得る。

【解決手段】 コンデンサ4,5の容量値C4,C5をC4>C5に設定したので、OTPセル1,2のいずれにも書き込みされていない場合、コンデンサ5の方がコンデンサ4よりも早く電位が上昇し、読み出し電圧確定回路の動作により書き込み読み出し線6は“L”、書き込み読み出し線7は“H”に読み出し出力が確定し、使用する回路を動作可能にする。また、OTPセル1に既に書き込みされており、その上、OTPセル2に書き込みされた場合に、コンデンサ5の方がコンデンサ4よりも早く電位が上昇し、読み出し電圧確定回路の動作により書き込み読み出し線6は“L”、書き込み読み出し線7は“H”に読み出し出力が確定し、書き込みを2回可能にする。

(もっと読む)

1 - 6 / 6

[ Back to top ]