国際特許分類[H01L27/102]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 複数の個々の構成部品を反復した形で含むもの (15,853) | バイポーラ構成部品を含むもの (10)

国際特許分類[H01L27/102]に分類される特許

1 - 10 / 10

半導体装置

【課題】微細化が可能であるメモリセル構造を備える半導体装置を提供する。

【解決手段】ワード線と、ビット線と、電源ノードと、ビット線と電源ノードとの間にPN結合を成す第1及び第2の領域並びに第2の領域とPN結合を成す第3の領域を少なくとも有するメモリ素子と、メモリ素子の第2の領域とは独立して設けられてメモリ素子の第2の領域と電気的に接続された第1の電極及び前記ワード線に接続された第2の電極を有するキャパシタと、を備える。

(もっと読む)

サイリスタベースメモリセル、デバイス及びそれらを含むシステム、そしてそれらを形成する方法

半導体デバイスは、複数のサイリスタベースメモリセルを含み、各々は、4F2のセルサイズを有し、そしてそれらの形成方法が提供される。前記複数のサイリスタベースメモリセルの各々は、垂直に重なる代替ドープされた領域を有するサイリスタ、と制御ゲートを含む。前記制御ゲートは、前記サイリスタの1つ又はそれ以上と電気的に結合されてもよく、そして電圧源に実施可能な接続がなされてもよい。前記複数のサイリスタベースメモリセルは、カソード又はデータ線として機能する伝導ストラップ上のアレイ内に形成されてもよい。システムは、相補型金属酸化膜半導体(CMOS)デバイスのような1つ又はそれ以上のメモリアクセスデバイス又は従来の論理デバイスを有する半導体デバイスを集積することによって形成されてもよい。  (もっと読む)

(もっと読む)

メモリ素子及びその製造方法

【課題】メモリ素子及びその製造方法を提供すること。

【解決手段】メモリ素子は、絶縁膜、アクティブパターン、ゲート絶縁膜、及びゲート電極を含む。前記絶縁膜は、基板上に形成される。前記アクティブパターンは、前記絶縁膜上に具備され、2つの突出部及びこれらの間の凹みを含む。前記アクティブパターンは、前記基板から離れた前記突出部の上部に形成された第1不純物領域及び第2領域不純物領域、並びに前記突出部の上部以外の部分に形成されデータを保存するフローティングボディの役割をするベース領域を含む。前記ゲート絶縁膜は前記アクティブパターンの表面に具備される。前記ゲート電極は、前記ゲート絶縁膜上に具備され、前記アクティブパターンの下部を取り囲んで前記凹みを部分的に埋める。

(もっと読む)

半導体装置およびその製造方法

【課題】サイリスタ構成の半導体装置において、第2p型領域上に第1n型領域、第1p型領域を積層して形成しても、第1p型領域と第2p型領域とがショートを起こさないようにすることを可能とする。

【解決手段】p型の第1p型領域p1(第1領域)と、n型の第1n型領域n1(第2領域)と、p型の第2p型領域p2(第3領域)と、n型の第2n型領域n2(第4領域)とが順に接合されたサイリスタT1が素子分離領域13で分離された半導体装置1であって、第2p型領域p2は、素子分離領域13で分離された半導体基板11に形成され、第1n型領域n1は、第2p型領域p2の一部上に形成されて、かつ、前記第1n型領域n1と第2p型領域p2との界面の一端部が素子分離領域11の側壁部に接合するように形成されていることを特徴とする。

(もっと読む)

半導体装置

【課題】読み出し動作時のディスターブの発生を抑止することが可能な半導体装置を提供する。

【解決手段】pnpn構造が形成されたゲート付きサイリスタ素子112と、半導体基板の半導体層に形成され、一端がビットラインに接続され、他端が上記サイリスタ素子の一端に接続されるアクセストランジスタ113と、を含むメモリセル111と、ビットラインの電圧がサイリスタ素子の特性を保持可能なモニタ電圧以下であるか否かをモニタし、ビットラインライン電圧がモニタ電圧以上となる場合には非活性化信号WLRESを出力するモニタ回路175と、メモリセルへのアクセス制御を行う制御部170等と、を有し、制御部170等は、読み出し動作時にモニタ回路による非活性化信号を受けると、アクセストランジスタをオフとするためにワードラインSWLへの駆動信号を非活性化する。

(もっと読む)

半導体装置

【課題】読み出し動作時のディスターブの発生を抑止することが可能な半導体装置を提供する。

【解決手段】基準電位端子が第2のビットラインRBLに接続されたゲート付きサイリスタ素子112と、一端が第1のビットラインWBLに接続されるアクセストランジスタと113、を含むメモリセル111と、読み出し時にサイリスタ素子の第2の端子(基準電位端子)に接続された第2のビットラインRBL側に負荷電流を流す負荷電流素子PT32を含み、メモリセルへのアクセス制御を行う制御部170と、を有し、制御部170は、読み出し動作時に、第1のビットラインWBLを第1の電圧に、第2のビットラインRBLを第1の電圧より高い第2の電圧に固定した状態で、第2のビットラインから第2の端子へ流れる電流変化を検知し、検知した電流を電圧に変換して読み出しデータの判定を行う。

(もっと読む)

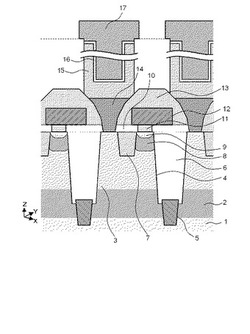

溝形チャネルの負性微分抵抗をベースとするメモリセル

ここには、改良型の溝形サイリスタベースセルが開示されている。本開示のセルは、一実施形態においては、基板のバルク内の溝に形成された導電性プラグを備えており、これはセルのイネーブルゲートに接続され、又はそれに含まれている。この溝形ゲートの周囲にはサイリスタが縦方向に配設され、そのアノード(ソース;p形領域)がビットラインに接続されると共に、カソード(ドレイン;n形領域)がワードラインに接続されている。この溝形イネーブルゲートの他には、本開示のセルはアクセストランジスタのような他のゲートを備えておらず、よって、本質的に1トランジスタデバイスである。その結果、サイリスタの縦方向配設によって容易になったように、本開示のセルは、伝統的なDRAMセルと比べて集積回路上に少量の領域だけを占有している。更に、本開示のセルは、その各種実施形態において製造が容易であり、セルアレイとして構成することも容易である。セル下の分離は、全ての有用な実施形態において必要とはされないが、セルのデータ保持を改善する助けになり、セルのリフレッシュ間に要する時間を延ばしてくれる。 (もっと読む)

半導体装置

【課題】アクセストランジスタとサイリスタとによってメモリセルが構成される半導体装置において、メモリセルの縮小化を可能とする。

【解決手段】アクセストランジスタ11と、前記アクセストランジスタ11に並列に接続された複数の負性抵抗特性の素子(サイリスタ)12,13とを備えたメモリセルを有するものであり、前記サイリスタはターンオンおよびターンオフを制御するゲート電極12G,13Gを有するものである。

(もっと読む)

半導体装置

【課題】安価なバルク半導体基板を用いて、縦型寄生サイリスタの発生を抑制すること、メモリセルサイズの縮小化を図ることを可能とする。

【解決手段】バルク半導体基板11に形成されたアクセストランジスタ40と、サイリスタ20と、両者を分離する素子分離領域13とを備え、アクセストランジスタ40の一方のソース・ドレイン領域45とサイリスタ20のカソード側のN型不純物層24とを接続孔52を通じて接続する配線層51を備え、前記サイリスタ20のアノード側の不純物領域は深さ方向にP型不純物層21、N型不純物層22、P型ウエル14(P型不純物層23)、N型ウエル12の順に形成された構造となっており、最下部のN型ウエル12にデータ保持時にアノードに印可する電圧と同じ電圧が印加されるものである。

(もっと読む)

メモリ

【課題】メモリセルサイズを小さくすることが可能なメモリを提供する。

【解決手段】このメモリは、p型シリコン基板11の主表面に形成され、メモリセル9に含まれるダイオード10のカソードおよびワード線7として機能するn型不純物領域12と、n型不純物領域12の表面に所定の間隔を隔てて複数形成され、ダイオード10のアノードとして機能するp型不純物領域14と、p型シリコン基板11上に形成され、p型不純物領域14に接続されるビット線8と、ビット線8よりも上層に設けられ、n型不純物領域12に対して所定の間隔ごとに接続される配線層27とを備えている。

(もっと読む)

1 - 10 / 10

[ Back to top ]