国際特許分類[H03K19/185]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 論理回路,すなわち,1出力に作用する少なくとも2入力を持つもの;反転回路 (4,821) | 特定の構成要素を用いるもの (1,730) | 可変誘電体定数をもつ誘電体素子を用いるもの,例.強誘電体コンデンサ (25)

国際特許分類[H03K19/185]の下位に属する分類

鉄共振装置を用いるもの (2)

国際特許分類[H03K19/185]に分類される特許

1 - 10 / 23

半導体チップ及びこれをパッケージングした半導体装置

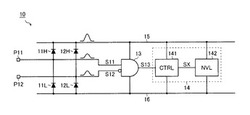

【課題】サージ印加時における内部回路の誤動作を防止する。

【解決手段】半導体チップ(10)は、複数のパッド(P11、P12)と、複数のパッド(P11、P12)と電源ライン(15、16)との間に接続された複数の静電破壊保護素子(11H、11L、12H、12L)と、複数のパッドのうち少なくとも2つのパッド(P11、P12)に現れる印加電圧(S11、S12)が同一の論理レベルか否かを監視するサージ検出部(13)と、サージ検出部(13)の検出結果(S13)に応じてその動作が許可/禁止される内部回路(14)と、を有する。

(もっと読む)

リセット回路およびシステム

【課題】 パワーオンまたはパワーダウンを検出するリセット回路を誤動作することなく動作させ、パワーオン時にリセット信号を正常に出力する。

【解決手段】 電源検出回路は、電源電圧が第1電圧を超えたときにパワーオン状態を示すパワーオン信号を活性化するとともに、初期化信号の活性化中に初期化される。スタータ回路は、電源電圧線と接地線の間に直列に配置された抵抗素子、遮断スイッチおよびキャパシタを有し、抵抗素子と遮断スイッチとを接続する第1接続ノードから初期化信号を出力する。遮断スイッチは、パワーオン信号の活性化中にオフする。このため、パワーオン状態中に、抵抗素子を介してキャパシタが充電されることを防止できる。この結果、キャパシタのTDDBの劣化を確実に防止でき、リセット回路を搭載する半導体装置およびシステムの誤動作を防止できる。

(もっと読む)

データ保持装置

【課題】通常動作時の速度低下や消費電力の増大を招くことなく、電源遮断後もデータを不揮発的に保持することが可能であり、かつ、信頼性や利便性の高いデータ保持装置を提供する。

【解決手段】データ保持装置は、ループ状に接続された複数の論理ゲートNAND3、NAND4を用いてデータを保持するループ構造部LOOPと、強誘電体素子のヒステリシス特性を用いてループ構造部LOOPに保持されたデータを不揮発的に記憶する不揮発性記憶部NVMと、ループ構造部LOOPと不揮発性記憶部NVMとを電気的に分離する回路分離部SEPと、複数の論理ゲートは、それぞれ、所定のセット信号SNL及びリセット信号RNLに応じて、任意の出力論理レベルにセット/リセットされるものであり、不揮発性記憶部NVMに記憶されたデータに基づいて、セット信号SNL及びリセット信号RNLを生成するセット/リセット制御部SRCを有する。

(もっと読む)

プログラマブルロジックデバイスおよびそれを用いた電子機器

【課題】複数の機能を短時間で切りかえ可能なPLDを提供する。

【解決手段】PLD100は、n(nは2以上の整数)個のコンテキストを切りかえ可能である。マルチコンテキストメモリ20は、n個のコンテキストを定義するn個のコンフィギュレーションデータCONF1〜CONFnを不揮発的に記憶する。(m×n)個のメモリセルMはそれぞれが対応する制御ラインCLおよび対応するビットラインBLに割り当てられている。メモリセルMは、対応する制御ラインCLが選択されたとき、対応するビットラインBLを介してアクセス可能となる。m個のセンスアンプは、対応するビットラインBLに生ずる信号を、リコンフィギュアラブル回路10に出力する。

(もっと読む)

半導体集積回路

【課題】書き込み回数に制限がなく、回路規模の増加に対して消費電力を抑制することができる半導体集積回路を提供する。

【解決手段】ルックアップテーブル101とフリップフロップ102Aのラッチ回路以外の回路構成部との電源供給経路を分離し、ルックアップテーブル101とラッチ回路以外の回路構成部とを別個に電源制御する電源コントローラ109及び電源制御回路111を備える。

(もっと読む)

プログラマブルロジックデバイスおよびそれを用いた信号処理回路

【課題】電源が遮断されても機能を維持可能なPLDを提供する。

【解決手段】リコンフィギュアラブル回路10は、その回路形態がコンフィギュレーションデータCONFに応じて設定される。コンフィギュレーションメモリ20は、リコンフィギュアラブル回路10と付随して設けられ、リコンフィギュアラブル回路10のコンフィギュレーションを設定するコンフィギュレーションデータCONFを保持する。コンフィギュレーションメモリ20は、コンフィギュレーションデータCONFの各データを保持する複数のメモリセルを含む。各メモリセルは、フリップフロップFFと、対応するフリップフロップの状態を保持する不揮発性メモリMnvを含む。複数のメモリセルのフリップフロップは、デイジーチェインを構成するように直列に接続され、コンフィギュレーションデータCONFが、当該デイジーチェインを経由してロード可能に構成されている。

(もっと読む)

カウンタ回路およびタイマー回路ならびにカウント方法および計時方法

【課題】最大カウント値を大きくすると、カウンタ回路の規模が増大する。

【解決手段】駆動部20は、所定のイベントが発生するごとに、所定回数、極性を交互に反転させながら強誘電体10に駆動電圧Vdrv1、Vdrv2を印加する。判定部30は、強誘電体10の分極量を測定し、イベントの発生回数を判定する。この判定部30は、電気的信号が印加されたことに起因する強誘電体10の疲労特性を利用して、経過時間が所定のしきい値を超えたか否かを判定する。

(もっと読む)

データ保持装置

【課題】通常時の速度低下や消費電力の増大を招くことなく、電源遮断後もデータを不揮発的に保持することが可能であり、かつ、どのような電源電圧を必要とするデバイスにも好適に組み込むことが可能なデータ保持装置を提供する。

【解決手段】データ保持装置において、ループ状に接続された論理ゲートを用いてデータを保持するループ構造部LOOPと、強誘電体素子のヒステリシス特性を用いてループ構造部LOOPに保持されたデータを不揮発的に記憶する不揮発性記憶部NVMは、互いに異なる電源電圧VDD1、VDD2の供給を別個に受けて駆動されるものであり、両者を電気的に分離する回路分離部SEPは、ループ構造部LOOPと不揮発性記憶部NVMとの間でやり取りされるデータの電圧レベルを変換するレベルシフタ(INV6、INV7)を有して成る。

(もっと読む)

遅延回路および半導体集積回路

【課題】 遅延時間が変更可能な不揮発性の遅延回路を提供する。

【解決手段】 強誘電体キャパシタの一端は、バッファ回路に接続される。強誘電体キャパシタの他端には、第1スイッチ回路を介して第1電圧が供給され、あるいは第2スイッチ回路を介して第1電圧と反対の論理レベルに対応する第2電圧が供給される。リセット制御回路は、リセット期間にバッファ回路に信号を出力することで強誘電体キャパシタの一端に第1電圧を与えるとともに、第1スイッチ回路をオフし、第2スイッチ回路をオンする第1スイッチ制御信号を出力する。また、リセット制御回路は、通常動作期間に第1スイッチ回路をオンし、第2スイッチ回路をオフする第2スイッチ制御信号を出力する。リセット期間に設定された分極値は電源がオフしても保持されるため、遅延時間が変更可能な不揮発性の遅延回路を実現できる。

(もっと読む)

半導体集積回路

【課題】ラッチ回路のデータ信号を強誘電体キャパシタに保持させる半導体集積回路において、強誘電体キャパシタのインプリント特性の劣化を防止すること。

【解決手段】データ信号Dを保持する信号保持部12と、信号保持部12にスイッチTR1、TR2を介して電気的に接続された強誘電体キャパシタF1、F2とを備えたラッチ回路10を有し、所定の期間内のみスイッチスイッチTR1、TR2をオン状態にし、データ信号Dの電位に応じた残留分極量を強誘電体キャパシタF1、F2に保持させる半導体集積回路による。

(もっと読む)

1 - 10 / 23

[ Back to top ]