国際特許分類[H03K19/21]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 論理回路,すなわち,1出力に作用する少なくとも2入力を持つもの;反転回路 (4,821) | 論理機能によって特徴づけられたもの,例.アンド,オア,ノア,ノット回路 (214) | 排他的オア回路,すなわち入力信号がただ一つのみ存在するとき出力を与えるもの;一致回路,すなわちすべての入力信号が等しいときのみ出力を与えるもの (43)

国際特許分類[H03K19/21]に分類される特許

1 - 10 / 43

論理回路及びデータ処理システム

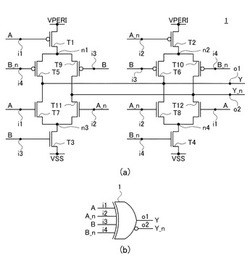

【課題】素子数が少なく、遅延が小さく、ドライバ能力を有するXORゲート回路を提供する。

【解決手段】論理回路1は、電源電位VPERIとノードn1の間に接続されたトランジスタT1と、電源電位VPERIとノードn2の間に接続されたトランジスタT2と、電源電位VSSとノードn3の間に接続されたトランジスタT3と、電源電位VSSとノードn4の間に接続されたトランジスタT4と、ノードn1とノードn3の間に直列接続されたトランジスタT5,T7と、ノードn1とノードn3の間に直列接続されたトランジスタT9,T11と、ノードn2とノードn4の間に直列接続されたトランジスタT6,T8と、ノードn2とノードn4の間に直列接続されたトランジスタT10,T12とを備える。出力信号Yは、トランジスタT5,T7の接続点及びトランジスタT6,T8の接続点から取り出される。

(もっと読む)

再構成可能な集積回路ユニットを備えた論理回路及びその論路回路のエラー修正方法

【課題】エラー箇所の特定を実施する際に、システムを停止しないでエラー発生前の高信頼性までシステム性能を復帰させる。

【解決手段】同一動作を行う複数個の再構成可能な集積回路ユニットを備え、複数の該集積回路ユニットのそれぞれに複数のバンクを有する論理回路において、入力されたデータを、複数個の前記集積回路ユニットの各バンクに振り分けて入力する入力データ制御部と、複数個の集積回路ユニットの各バンクから出力されるデータを比較して、データ間の不一致を検出するエラー解析部と、エラー解析部から、データ間の不一致の通知を受けた場合に、複数個の集積回路ユニットの該当するバンクの再構成を行う構成情報制御部と、を備える。

(もっと読む)

ラッチ回路、トリミング回路、システム、判定プログラム、確認方法、及び判定方法

【課題】入力信号の状態が適正であるかを確認することができる、ラッチ回路、トリミング回路、システム、判定プログラム、確認方法、及び判定方法を提供する。

【解決手段】トリミング回路14の読出回路20から出力されるトリミング素子であるヒューズ素子H1の状態に応じた入力信号I1が入力されるラッチ回路22を、ラッチ回路L1と、ラッチ回路L2と、一致確認回路26と、で構成している。ラッチ回路L1は、入力信号I1の論理値をタイミングT1で保持して、保持した論理値に応じた出力信号O1をトリミング回路14の外部に出力する。ラッチ回路L2は、タイミングT1よりも遅いタイミングT2で保持して、保持した論理値に応じた出力信号O2を出力する。一致確認回路26は、排他的論理和回路30により構成されており、出力信号O1と出力信号O2とが一致しているか否かを示す一致判定信号X1を外部の判定回路18に出力する。

(もっと読む)

半導体装置

【課題】耐タンパ性を有する、可変論理機能を実現するための記憶回路を有する半導体装置を提供する。

【解決手段】制御回路24は、記憶回路23の次の読出しアドレスを先に記憶回路23から読出した制御フィールドの情報または外部イベント入力に基づいて自律的に制御することが可能である。正規デコーダ28は、制御回路24から出力されるアドレスをデコードし、デコード結果に基づいて、データフィールドの少なくとも1つの正規メモリセルと、制御フィールドの少なくとも1つのメモリセルを選択する。冗長制御回路51は、イネーブル信号が活性化された場合に限り、制御回路24から出力されるアドレスと、所定の正規メモリセルのアドレスとが一致したときに、正規デコーダ28による選択を禁止し、データフィールドの少なくとも1つの冗長メモリセルと制御フィールドの少なくとも1つの冗長メモリセルを選択する。

(もっと読む)

半導体集積回路

【課題】より信頼性の高い半導体集積回路を提供すること。

【解決手段】本発明にかかる半導体集積回路は、入力信号DINを記憶保持する複数のフリップフロップF1と、複数のフリップフロップF1からの出力の多数決結果MJを出力する多数決回路7と、複数のフリップフロップF1の出力不一致を検出し、エラー信号を出力するエラー検出回路2と、エラー検出回路2からのエラー信号を監視する監視回路3と、を備え、監視回路3は、エラー検出回路2からのエラー信号をもとに、複数のフリップフロップF1のうち、出力不一致が発生しているフリップフロップF1に対して書き戻しを行うリフレッシュ動作を指示するとともに、リフレッシュ動作により書き戻らなかった場合には外部に通知を行うものである。

(もっと読む)

論理回路

【課題】伝播遅延時間の短縮を図り高速化に対応可能とした論理回路の提供。

【解決手段】論理信号をそれぞれ入力とする第1及び第2の入力端子A、Bを有し、ソースがそれぞれに対応する第1及び第2の入力端子A、Bに接続され、ゲートが、第2及び第1の入力端子B、Aに交差接続された第1及び第2のMOSトランジスタNM1、NM2を備え、第1及び第2のMOSトランジスタNM1、NM2のドレインが共通接続され、第1の電源VDDと、第1及び第2のMOSトランジスタNM1、NM2のドレインの共通ノードN1との間に接続され、リセット信号/RESETをゲートに受けリセット時に導通するMOSトランジスタPM1を備え、さらに共通ノードN1を入力端に接続してなるインバータINVを備えている。

(もっと読む)

XOR及びXNORロジックの回路及びレイアウト

XOR回路は、第2の入力ノードによって制御されるパスゲートを備える。そのパスゲートは、制御されたとき、第1の入力ノードに存在するロジック状態のバージョンを出力ノードに通すように接続されている。伝送ゲートが、第1の入力ノードによって制御される。その伝送ゲートは、制御されたときに、第2の入力ノードに存在するロジック状態のバージョンを出力ノードに通すように接続されている。プルアップロジックが、第1及び第2の入力ノードの両方によって制御される。そのプルアップロジックは、第1及び第2の入力ノードの両方がハイのときに、出力ノードをロウに駆動するように接続されている。XNOR回路は、プルアップロジックが、第1及び第2の入力ノードの両方がハイときに出力ノードをハイに駆動するように接続されたプルダウンロジックに置換されることを除いて、XOR回路と同様に画定される。  (もっと読む)

(もっと読む)

予備充電ロジックにおけるエラー検出

【課題】内蔵のエラー検出回路を持ったドミノロジックのような予備充電されたロジックを含む集積回路を提供すること。

【解決手段】推論ノード22と検査ノード24とを含むドミノロジックを持つ集積回路2が提供される。予備充電回路36は、推論ノードと検査ノードの両方を予備充電する。論理回路26は、入力信号値に基づいて推論ノードと検査ノードとのため放電路を提供する。評価制御回路28,30は、先ず推論ノードを論理回路に結合し、次いで検査ノードを論理回路に結合するので、もし論理回路26への入力信号が適切な値を持つなら、これらは放電されうる。推論ノードと検査ノードとが両方とも放電されるか又は両方とも放電されないかのいずれでもない場合に、エラー検出回路32はエラーを検出する。

(もっと読む)

電子回路

【課題】消費電力の少ない電子回路を提供する。

【解決手段】第1内部クロック信号CLK1の論理値に応じて信号を通過または保持する第1ラッチ回路11と、第1ラッチ回路11に従属接続され、第1ラッチ回路11と逆の動作特性により第1内部クロック信号CLK1の論理値に応じて信号を通過または保持する第2ラッチ回路12とを有する第1ラッチ回路群13と、第1ラッチ回路11の信号入力端における信号の論理値と第2ラッチ回路12の信号出力端における信号の論理値とを比較し、第1ラッチ回路11の信号入力端における信号の論理値と第2ラッチ回路12の信号出力端における信号の論理値とが同一の場合は一定の論理値信号を第1内部クロック信号CLK1として出力し、異なる場合はクロック信号CLKを第1内部クロック信号CLK1として出力する第1クロック制御手段14とを具備している。

(もっと読む)

半導体集積回路

【課題】エラー検出のためのハードウエア上のオーバーヘッド及び時間的オーバーヘッドを小さくでき、且つエラーを発生した論理素子を特定できる半導体集積回路を提供することを第1目的とする。また、ダイナミック回路のリセット時間による時間的オーバーヘッドを隠蔽でき、実効的な演算スループットを向上させる半導体集積回路を提供することを第2目的とする。

【解決手段】本発明に係る半導体集積回路は、論理素子単位でのハンドシェークを実施し、論理素子単位でのエラー発生の検出を行うことで後段の論理素子にエラー伝搬を行わないこととした。さらに、本発明に係る半導体集積回路は、各論理素子内で同一の論理回路を並列に接続し、2相で動作させることとした。

(もっと読む)

1 - 10 / 43

[ Back to top ]