国際特許分類[H03K3/80]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電気的パルスの発生回路;単安定回路,双安定回路,多安定回路 (1,702) | 正弦波振動の列の発生 (5)

国際特許分類[H03K3/80]に分類される特許

1 - 5 / 5

波形発生器及びそれを備えた信号発生装置並びに波形発生方法及び信号発生方法

【課題】各ビットデータの周波数オフセットの発生を低減しつつ、波形パターン列の接続部の位相を連続にすることができる波形発生器及びそれを備えた信号発生装置並びに波形発生方法及び信号発生方法を提供する。

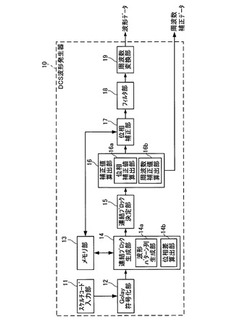

【解決手段】DCS波形発生器10は、波形パターンのブロックデータを生成するGolay符号化部12と、メモリ部13の記憶容量の範囲内で記憶可能な個数だけ波形パターンのブロックデータを連結した波形パターンブロック列を生成する波形パターン列生成部14aと、波形パターンブロック列の先頭の波形パターンのブロックデータから位相差が最小となる波形パターンのブロックデータまでを生成波形データとして決定する連結ブロック決定部15と、接続部位相差をゼロにする分配位相補正値を算出する位相補正値算出部16aと、周波数オフセットを算出する周波数補正値算出部16bと、を備える。

(もっと読む)

交流信号発生装置

【課題】簡単な構成で減衰交流信号を発生させることが可能な交流信号発生装置を提供すること。

【解決手段】交流信号発生装置は、周波数が僅かに異なる2つの矩形波を発生させる矩形波発生手段として機能するマイクロコンピュータと、2つの矩形波を入力し、一方の矩形波の電圧値から他方の矩形波の電圧値を減算した差を出力する両極性の差動増幅回路と、アクティブフィルター回路によって構成され、交流信号を出力する低域通過型フィルター回路とを備える。マイクロコンピュータは、2つの矩形波の初期の位相差が180度であり、2つの矩形波の位相差が0になる時点で矩形波の発生を終了する。特に減衰のための回路を必要とせず、外付け部品等による影響を殆ど受けずに安定した減衰信号が得られる。

(もっと読む)

信号発生回路、ジッタ印加回路、半導体チップ、及び試験装置

【課題】ジッタが印加された出力信号を生成する信号発生回路200。

【解決手段】ジッタが印加された出力信号を生成する信号発生回路であって、周波数の異なる第1ジッタ信号及び第2ジッタ信号を出力するジッタ出力部と、第1ジッタ信号及び第2ジッタ信号の略中間の周波数のキャリア信号を出力するキャリア出力部と、第1ジッタ信号、第2ジッタ信号、及びキャリア信号を加算して、出力信号を生成する加算部とを備える信号発生回路。

(もっと読む)

パルス発生器及びそれを用いた送信機

【課題】 UWB伝送用パルス発生器における構成の簡易化、低消費電力化と、LO信号を使わないことによるLOリークの抑制。

【解決手段】 所定の周期のクロックを与えるクロック発生装置(CLK)と、遅延時間制御機能を持ち前記クロックを遅延させる遅延回路(DLY)と、前記遅延回路から出力される遅延時間の異なる信号同士を比較することで遅延回路一段分の遅延時間差に相当するパルス幅を持つ方形波パルスを、拡散符号により拡散された情報を受け取ることで位相を変調して出力する方形波パルス発生回路(SWPG)と、前記方形波パルス発生回路から異なるタイミングで出力される方形波パルス列を受け取ることにより、前記方形波のパルス幅を持ち所定の振幅でインパルス列を出力し、重ね合わせる振幅制御ユニット(AMPC)を有し、所定の包絡線形状を有するパルスを生成する。

(もっと読む)

広帯域ダイレクト・ディジタル・シンセサイザ

信号発生器、及び周波数シンセサイザのDDSは比較的高い入力クロックスピードを必要とし、不要な成分が出力周波数スペクトルの中に存在するスプリアス周波数応答を生成する。DDSへのクロック信号入力を変化させることによりスプリアスDDS応答を減少させるか回避するためのシステム及び方法を提供する。 (もっと読む)

1 - 5 / 5

[ Back to top ]