国際特許分類[H03M1/74]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 符号化,復号化または符号変換一般 (10,763) | アナログ/デジタル変換;デジタル/アナログ変換 (2,647) | デジタル/アナログ変換器 (612) | 同時変換 (311)

国際特許分類[H03M1/74]の下位に属する分類

スイッチングツリーを用いるもの (82)

ラダー回路網を用いるもの (29)

重みづけられたインピーダンスを用いるもの (7)

国際特許分類[H03M1/74]に分類される特許

1 - 10 / 193

デジタル−アナログ変換器及びそのような変換器を用いた神経形態学的回路

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

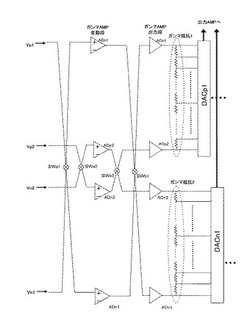

液晶表示装置の駆動装置

【課題】オフセットの影響、回路規模の増大、フリッカ等を抑制し、画質の向上に好適なドライバの提供。

【解決手段】切換制御信号が第1の論理値のとき、第1、第3の電圧が第1、第3の差動段に、第2、第4の電圧が第2、第4の差動段に入力され、第1、第3の差動段の出力が第1、第3の出力段の入力に、第2、第4の差動段の出力が第2、第4の出力段の入力にそれぞれ接続され、ガンマ抵抗1両端には第1、第2の電圧が、ガンマ抵抗2両端には第3、第4の電圧が印加され、切換制御信号が第2の論理値のとき、第1、第3の電圧が第3、第1の差動段に、第2、第4の電圧が第4、第2の差動段に入力され、第3、第1の差動段の出力が第1、第3の出力段の入力に、第4、第2の差動段の出力が第2、第4の出力段の入力にそれぞれ接続され、ガンマ抵抗1両端には第1、第2の電圧が、ガンマ抵抗2両端には第3、第4の電圧が印加される。

(もっと読む)

デジタル−アナログ変換器及び半導体集積回路

【課題】デジタル−アナログ変換器の低電圧動作を実現するとともにミラー電流精度を高める。

【解決手段】デジタル−アナログ変換器10は、基準電流を所定のミラー比で複製する第1トランジスタと前記第1トランジスタにカスコード接続される第2トランジスタとを含むミラー回路と、前記第2トランジスタのゲートに接続され、外部からの入力されるデジタル入力信号によってオン・オフ制御されるアナログスイッチとを含む。

(もっと読む)

逐次比較型AD変換器および無線受信機

【課題】容量DA変換器を駆動するドライバを低消費電力化しつつ、低誤差のAD変換を行う。

【解決手段】バイナリ重み型容量DA変換器は、アナログ入力信号と、参照電圧とに基づき、Nビットの各ビットに対応するサイクル毎に、残差信号を生成する。第1比較器は、前記サイクル内の第1の時点における前記残差信号を、所定電圧と比較して、論理値を表す第1比較結果を得る。レジスタは、前記第1比較結果を保持する。第2比較器は、前記サイクル内における前記第1の時点より後の第2の時点における前記残差信号を、前記所定電圧と比較して、論理値を表す第2比較結果を得る。誤り判定回路は、前記第1比較結果が前記第2比較結果と異なるとき、誤り検出信号を発生させる。誤り訂正回路は、前記誤り判定回路により前記誤り検出信号が発生させられたとき、前記レジスタから読み出し第1比較結果を反転して出力する。

(もっと読む)

電源回路

【課題】カレントミラー回路によって、複数の回路を電流駆動させる場合に、各回路の動作に対するばらつきを低減することができる電源回路を提供する。

【解決手段】FET1、2、3と、スイッチング素子であるスイッチ6〜9とで電源回路を構成している。FET1、2、3でカレントミラー回路を構成している。スイッチ6、7、8、9によって選択回路50が構成される。選択回路50は、スイッチ6〜9の切り替えにより、ミラー電流Ib2をオペアンプ4又はオペアンプ5のいずれかに供給し、さらに、ミラー電流Ib1をオペアンプ4又はオペアンプ5のいずれかに供給する。すなわち、ミラー電流Ib1とミラー電流Ib2とを入れ替えて交互に、オペアンプ4、5にそれぞれ供給する。

(もっと読む)

デジタル/アナログ変換器

【課題】消費電流を低減しつつ、出力信号の歪みを低減することが可能なデジタル/アナログ変換器を提供する。

【解決手段】デジタル/アナログ変換器において、第1の容量制御用スイッチ素子は、第1のMOSトランジスタがオンするときオフし、一方、前記第1のMOSトランジスタがオフするときオンする。さらに、デジタル/アナログ変換器において、第2の容量制御用スイッチ素子は、第2のMOSトランジスタがオンするときオフし、一方、前記第2のMOSトランジスタがオフするときオンする。

(もっと読む)

ディジタル/アナログ変換器

【課題】入出力特性として非線形な特性を精度良く実現することができるディジタル/アナログ変換器を提供する。

【解決手段】コード変換部4が、ディジタル入力信号の最上位ビットと残りの(N−1)ビットそれぞれとの排他的論理輪演算を行い、(N-1)ビットの第1の演算結果を出力する第1のゲート回路4Aと、第1の演算結果を{2(N−1)−1}ビットの温度計・コードにデコードするデコーダ1Aと、デコードされた温度計・コードの{2(N−1)−1}ビットそれぞれとディジタル入力信号の最上位ビットとの排他的論理輪演算を行い、{2(N−1)−1}ビットの第2の演算結果を出力する第2のゲート回路4Bとを備える。

(もっと読む)

D/A変換回路、A/D変換回路及び電子機器

【課題】レイアウト効率の向上や回路特性の向上等を実現できるD/A変換回路、A/D変換回路、電子機器等の提供。

【解決手段】D/A変換回路は、出力ノードに接続される第1のD/A変換部DAC1と、出力ノードと第1のノードとの間に設けられる第1の直列キャパシターCS1と、第1のノードに接続される第2のD/A変換部DAC2と、出力ノードと第2のノードとの間に設けられる第2の直列キャパシターCS2と、第2のノードに接続される第1のサブD/A変換部SDAC1と、スイッチ制御を行う制御回路を含む。第2のD/A変換部DAC2の第2のキャパシターアレイ部CAR2と第1のサブD/A変換部SDAC1の第1のサブD/A用キャパシターアレイ部SCAR1とが、第1のD/A変換部DAC1の第1のキャパシターアレイ部CAR1を通る対称軸LXに対して線対称に配置される。

(もっと読む)

電圧発生回路、共振回路、通信装置、通信システム、ワイヤレス充電システム、電源装置、及び、電子機器

【課題】 可変容量素子の容量を制御するための制御電圧を発生する電圧発生回路において、より簡易で、かつ、より低価格な構成を提供する。

【解決手段】 電圧発生回路3を、抵抗回20と、複数の入力ポート11〜18と、出力ポート30とで構成する。抵抗回路20は、複数の抵抗21〜27を有し、複数の抵抗21〜27を直列又は並列に接続して構成される。複数の入力ポート11〜18には、電位状態をハイ状態、ロー状態及び開放状態のいずれかに制御する制御信号がそれぞれ入力される。そして、出力ポート30は、複数の入力ポート11〜18のそれぞれの電位状態の組み合わせに対応した電圧値の電圧信号Vcを出力する。

(もっと読む)

D/A変換回路、A/D変換回路及び電子機器

【課題】見かけ上の容量比精度を高めて変換精度を向上できるD/A変換回路、及びこれを含むA/D変換回路、電子機器等の提供。

【解決手段】D/A変換回路は、出力ノードに一端が接続される複数のキャパシターを有するキャパシターアレイ部41と、キャパシターアレイ部41の複数のキャパシターの他端に接続され入力デジタルデータに応じてスイッチ制御される複数のスイッチ素子を有するスイッチアレイ部51と、スイッチアレイ部51のスイッチ制御を行う制御回路20を含む。キャパシターアレイ部41には、第1型キャパシター1Cと、第1型キャパシター1Cとは容量値が異なる第2型キャパシター3Cとが設けられる。制御回路20は、入力デジタルデータの各ビットに対する第1型キャパシター1Cと第2型キャパシター3Cの割り当てを動的に変化させるスイッチ制御をスイッチアレイ部51に対して行う。

(もっと読む)

1 - 10 / 193

[ Back to top ]