インダクタンス素子

【課題】 異なる複数の幅のランド電極のいずれにも実装可能なインダクタンス素子を提供する。

【解決手段】 インダクタンス素子100は、巻芯部の両端部に形成された上鍔部2および下鍔部3を備えたコア1と、巻芯部に巻回された導線4と、下鍔部3に形成された1対の端子電極5を備え、下鍔部3は、内面と、底面3aと、1対の側面3bと、1対の端面3cを備え、端子電極5は、主電極領域5aと、主電極領域5aから1対の側面3b方向にそれぞれ延びた少なくとも1対の延長電極領域5bを備え、導線4の両端部4aは、それぞれ、下鍔部3の側面3bおよび底面3aを経由して、端子電極5に接続され、下鍔部3の底面3aの、導線4の両端部4aが経由する領域には、端子電極5の延長電極領域5bが形成されないようにした。

【解決手段】 インダクタンス素子100は、巻芯部の両端部に形成された上鍔部2および下鍔部3を備えたコア1と、巻芯部に巻回された導線4と、下鍔部3に形成された1対の端子電極5を備え、下鍔部3は、内面と、底面3aと、1対の側面3bと、1対の端面3cを備え、端子電極5は、主電極領域5aと、主電極領域5aから1対の側面3b方向にそれぞれ延びた少なくとも1対の延長電極領域5bを備え、導線4の両端部4aは、それぞれ、下鍔部3の側面3bおよび底面3aを経由して、端子電極5に接続され、下鍔部3の底面3aの、導線4の両端部4aが経由する領域には、端子電極5の延長電極領域5bが形成されないようにした。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、インダクタンス素子に関し、更に詳しくは、異なる複数の幅のランド電極のいずれにも実装可能なインダクタンス素子に関する。

【背景技術】

【0002】

各種電子機器に用いるインダクタンス素子として、ドラム型のコアに導線を巻回し、導線の両端部をコアに形成した端子電極に接続した構造からなるものが広く使用されている。

【0003】

たとえば、特許文献1(特開平2010‐171054号公報)に、そのような構造からなる従来のインダクタンス素子が開示されている。図9に、特許文献1に開示されたインダクタンス素子800を示す。

【0004】

インダクタンス素子800は、ドラム型のコア101を備える。コア101は、巻芯部(図示せず)の両端部に、上鍔部102、下鍔部103が形成された構造からなる。なお、図9においては、説明の都合上、インダクタンス素子800を上下逆に、すなわち、上鍔部102を下に、下鍔部103を上に示している。

【0005】

下鍔部103は、巻芯部側の内面(図示せず)と、底面103aと、1対の側面103bと、1対の端面103cを備えている。なお、側面103bは、複数の面が連なった形状からなる。

【0006】

また、コア101の巻芯部には、絶縁被覆が施された導線104が巻回されている。

【0007】

更に、コア101の下鍔部103の底面103aには、1対の端子電極105、105が形成されている。そして、導線104の両端部104a、104aが、それぞれ、下鍔部103の側面103bおよび底面103aを経由して、事前に絶縁被覆が剥離されたうえで、端子電極105、105に接続されている。

【0008】

なお、インダクタンス素子800においては、下鍔部103の底面103aに1対の溝103d、103dが形成され、溝103d、103dに導線104の両端部104a、104aが収容されている。また、端子電極105、105は、下鍔部103の底面103aに凹部(図示せず)を設け、その中にはんだを埋め込んだものからなる。しかしながら、溝103b、103bは必ずしも必要ではない。また、端子電極105、105は、凹部にはんだを埋め込んだものではなく、下鍔部103の底面103aに銀ペーストを焼付けるなどして形成したものの方が一般的である。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開平2010‐171054号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

しかしながら、上述した従来のインダクタンス素子800には、クリームはんだなどを使ったリフローはんだにより実装した場合に、特定の幅のランド電極には適切に実装できるが、それ以外の幅のランド電極には適切に実装できないという問題があった。

【0011】

すなわち、インダクタ素子に限らず、電子部品においては、その製造者や販売者(以下、「製造者等」という)により、推奨するランド電極の寸法が示される場合が多い。たとえば、製造者等であるA社では、図10(A)に示すように、幅1.0mm×長さ0.9mmの1対のランド電極(以下「幅狭ランド電極201」という)を、0.8mm間隔で対向させたものをランド電極として推奨し、それに合致した端子電極を備えたインダクタンス素子を製造、販売している。一方、別の製造者等であるB社では、図10(B)に示すように、幅1.6mm×長さ0.65mmの1対のランド電極(以下「幅広ランド電極202」という)を、0.7mm間隔で対向させたものをランド電極として推奨し、それに合致した端子電極を備えたインダクタンス素子を製造、販売している。

【0012】

なお、インダクタンス素子の実装は、基板などに形成された幅狭ランド電極201、201、または幅広ランド電極202、202の表面に、クリームはんだなどを塗布したうえで、インダクタンス素子を配置し、基板ごとトンネル炉などに入れて加熱し、続いてトンネル炉などから取出し冷却することによりおこなわれる。

【0013】

インダクタンス素子800は、端子電極105の幅が約1.0mmに形成されているため、図11(A)に示すように、幅狭ランド電極201、201には、適切に実装することができる。(図11(A)においては、幅狭ランド電極201のインダクタンス素子800に隠れた部分を破線で示すとともに、インダクタンス素子800の底面に形成されているために見えない端子電極105をハッチング付きの破線で示している。以下、図11(B)、図13(A)、(B)において、同様の示し方をしている。)

しかしながら、インダクタンス素子800を幅広ランド電極202、202に実装しようとすると、図11(B)に示すように、インダクタンス素子800が幅広ランド電極202、202上で回転してしまうことがあった。加熱してクリームはんだが溶融した際に、インダクタンス素子800の位置が安定せずに流動してしまったことによる。

【0014】

幅広ランド電極202、202にインダクタンス素子を適切に実装するためには、端子電極の幅を広く形成しなければならなかった。図12に、インダクタンス素子800の端子電極105の幅を広く設計変更した、別の従来のインダクタンス素子900を示す。

【0015】

インダクタンス素子900においては、端子電極115の幅が、約1.6mmに形成されている。インダクタンス素子900の他の構成は、上述したインダクタンス素子800と同じである。

【0016】

この結果、インダクタンス素子900は、図13(A)に示すように、幅広幅狭ランド電極201、201には、適切に実装することができる。

【0017】

しかしながら、インダクタンス素子900を幅狭ランド電極201、201に実装しようとすると、図13(B)に示すように、インダクタンス素子900が幅狭ランド電極201、201の片側にシフトしてしまうことがあった。加熱してクリームはんだが溶融した際に、インダクタンス素子900の位置が安定せずに流動してしまったことによる。

【0018】

このように、従来のインダクタンス素子800、900においては、クリームはんだなどを使ったリフローはんだにより実装した場合に、特定の幅のランド電極には適切に実装できるが、それ以外の幅のランド電極には適切に実装できないという問題があった。すなわち、A社とB社で推奨するランド電極の寸法が異なる場合、A社の推奨するランド電極にはA社のインダクタンス素子しか実装できず、B社の推奨するランド電極にはB社のインダクタンス素子しか実装できず、相互に互換性がないという問題があった。

【0019】

なお、端子電極115の幅を大きくした従来のインダクタンス素子900においては、導線104の断線を発見しにくいという別の問題もあった。すなわち、導線104の端部104aは、下鍔部103の側面103bを経由して、下鍔部103の底面103aに形成された端子電極115に接続されるが、導線104は、下鍔部103の側面103bと底面103aが形成する辺の近傍おいて断線しやすい。しかしながら、下鍔部103の底面103aにおいて、側面103bと底面103aが形成する辺の近傍に、幅を大きくした端子電極115が存在すると、目視による検査において、この部分における導線104の断線を見落としてしまいやすいという問題があった。すなわち、絶縁被覆が剥離された導線104と、端子電極115は、両者とも金属色であるため、導線104が断線しているにもかかわらず、断線していないように誤認してしまうことがあった。

【課題を解決するための手段】

【0020】

本発明は、上述した従来のインダクタンス素子の有する問題を解決するためになされたものであり、その手段として本発明のインダクタンス素子は、巻芯部と、その巻芯部の両端部に形成された上鍔部および下鍔部を備えたコアと、巻芯部に巻回された導線と、下鍔部に形成された1対の端子電極を備え、下鍔部は、内面と、底面と、1対の側面と、1対の端面を備え、1対の端子電極は、それぞれ下鍔部の底面に形成された主電極領域と、その主電極領域から下鍔部の1対の側面方向にそれぞれ延びた少なくとも1対の延長電極領域を備え、導線の両端部は、それぞれ下鍔部の側面および底面を経由して、端子電極に接続され、下鍔部の底面における導線の両端部が経由する領域には、端子電極の延長電極領域が形成されないようにした。

【0021】

なお、下鍔部の側面に、導線を経由させるための凹部を形成しても良い。この場合には、製造時や実装時などにおいて、下鍔部の側面に予期せず物体(装置、冶具、他の電子部品など)が衝突しても、導線が断線してしまうことがない。

【0022】

また、1対の端子電極は、それぞれ下鍔部の端面に、更に端面電極領域を備えるようにしても良い。この場合には、端面電極領域とランド電極の間にはんだフィレットを形成することができるため、強固な接合を実現することができる。

【0023】

また、端子電極の延長電極領域は、それぞれ途中に段部が形成され、主電極領域から下鍔部の側面に向かう方向に異なる複数の長さを備えるようにしても良い。たとえば、延長電極領域が異なる2つの長さを備える場合には、主電極領域と延長電極領域で、合計3つの異なる幅のランド電極のいずれにも実装することが可能になる。

【0024】

また、端子電極の延長電極領域は、それぞれ下鍔部の底面と側面が形成する辺にまで至って形成されるようにしても良い。

【発明の効果】

【0025】

本発明のインダクタンス素子は、主電極領域と、その主電極領域から、下鍔部の1対の側面方向にそれぞれ延びた少なくとも1対の延長電極領域を備えるようにしたため、複数の異なる幅のランド電極のいずれにも実装が可能になっている。

【0026】

また、本発明のインダクタンス素子は、下鍔部の底面の導線の両端部が経由する領域に、端子電極の延長電極領域を設けないようにしているため、この近傍で導線が断線した場合には、容易に発見することができる。

【図面の簡単な説明】

【0027】

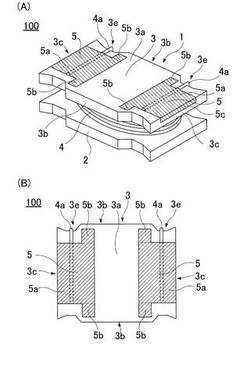

【図1】図1(A)は、本発明の第1実施形態にかかるインダクタンス素子100を示す斜視図である。図1(B)は、インダクタンス素子100を示す底面図である。

【図2】図2(A)は、インダクタンス素子100を幅狭ランド電極201に実装した状態を示す平面図である。図2(B)は、インダクタンス素子100を幅広ランド電極202に実装した状態を示す平面図である。

【図3】本発明の第2実施形態にかかるインダクタンス素子200を示す底面図である。

【図4】本発明の第3実施形態にかかるインダクタンス素子300を示す底面図である。

【図5】本発明の第4実施形態にかかるインダクタンス素子400を示す底面図である。

【図6】本発明の第5実施形態にかかるインダクタンス素子500を示す底面図である。

【図7】本発明の第6実施形態にかかるインダクタンス素子600を示す底面図である。

【図8】本発明の第7実施形態にかかるインダクタンス素子700を示す底面図である。

【図9】従来のインダクタンス素子800を示す斜視図である。

【図10】図10(A)は、幅狭ランド電極201を示す平面図である。図10(B)は、幅広ランド電極202を示す平面図である。

【図11】図11(A)は、インダクタンス素子800を幅狭ランド電極201に実装した状態を示す平面図である。図11(B)は、インダクタンス素子700を幅広ランド電極202に実装した状態を示す平面図である。

【図12】別の従来のインダクタンス素子900を示す斜視図である。

【図13】図13(A)は、インダクタンス素子900を幅広ランド電極202に実装した状態を示す平面図である。図13(B)は、インダクタンス素子900を幅狭ランド電極201に実装した状態を示す平面図である。

【発明を実施するための形態】

【0028】

以下、図面とともに、本発明を実施するための形態について説明する。

【0029】

[第1実施形態]

図1(A)、(B)に、本発明の第1実施形態にかかるインダクタンス素子100を示す。ただし、図1(A)は斜視図、図1(B)は底面図である。

【0030】

インダクタンス素子100は、フェライトなどからなるドラム型のコア1を備える。コア1は、巻芯部(図示せず)の両端部に、上鍔部2、下鍔部3が形成された構造からなる。なお、図1(A)においては、説明の都合上、インダクタンス素子100を上下逆に、すなわち、上鍔部2を下に、下鍔部3を上に示している。コア1は、フェライトなどの磁性体で形成されていても良いし、アルミナなどの非磁性体で形成されていても良い。

【0031】

下鍔部3は、巻芯部側の内面(図示せず)と、内面の裏側の底面3aと、1対の側面3bと、1対の端面3cを備えている。なお、側面3bは、複数の面が連なった形状で構成されており、それらの面により、後述する導線4を経由させるための凹部3eが形成されている。

【0032】

また、コア1の巻芯部には、ポリウレタンなどの絶縁被覆が施された、Cu、Agなどからなる導線4が巻回されている。

【0033】

更に、コア1の下鍔部3の底面3aには、1対の端子電極5、5が形成されている。端子電極5、5は、たとえば、銀ペースト、銅ペーストなどを焼付けることにより形成されている。

【0034】

各端子電極5は、下鍔部3の底面3aに、主電極領域5aと、主電極領域5aから下鍔部3の1対の側面3b方向にそれぞれ延びた少なくとも1対の延長電極領域5b、5bを備える。更に、各端子電極5は、下鍔部3の端面3cに、端面電極領域5cを備える。なお、図1(B)においては、主電極領域5aと延長電極領域5bの間に破線を示しているが、これは説明のために示したものであり、実際には両者は一体的に形成されている。

【0035】

主電極領域5aは、図9(A)に示した、幅狭ランド電極201への実装を可能にする役割をはたすもので、約1.0mmの幅をもつ。一方、延長電極領域5b、5bは、図9(B)に示した、幅広ランド電極202への実装を可能にする役割をはたすもので、一方の延長電極領域5bの端から、他方の延長電極領域5bの端までは、約1.6mmの幅をもつ。そして、端面電極領域3cは、ランド電極との間にはんだフィレットを形成し、接合を強固にするとともに、実装位置を適正に調整するためのものである。

【0036】

そして、導線4の両端部4a、4aが、それぞれ、下鍔部3の側面3bおよび底面3aを経由して、事前に絶縁被覆が剥離されたうえで、端子電極5、5に接続されている。

【0037】

本発明においては、下鍔部3の底面3aにおける、導線4の端部4aと端子電極5の接続部分近傍に、端子電極5の延長電極領域5bが形成されておらず、下鍔部3の底面3aの素地がそのまま露出しているため、下鍔部3の側面3bと底面3aが形成する辺の近傍において導線4が断線しても、容易に断線を発見することができる。したがって、不良品が、良品と誤って出荷されてしまうようなことがない。

【0038】

なお、本実施形態においては、下鍔部3の側面3bが複数の面が連なった形状で構成され、それらの面により、側面3bに凹部3eが形成されている。したがって、凹部3eを経由させることにより、導線4の下鍔部3の側面3bにおける経由位置が安定している。

【0039】

かかる構造からなる、本発明の第1実施形態にかかるインダクタンス素子100は、たとえば、次の方法により製造される。

【0040】

まず、巻芯部の両端に上鍔部2と下鍔部3を備えた、ドラム型のコア1を作製する。具体的には、フェライト、アルミナなどの粉末を、所定の形状からなる金型に充填し、加圧して成形体を得る。続いて、その成形体を、所定のプロファイルで焼成して、コア1を得る。

【0041】

次に、コア1に、1対の端子電極5、5を形成する。具体的には、コア1の下鍔部3の底面3aおよび端面3cに、銀ペーストあるいは銅ペーストを所望の形状に印刷し、焼付けて形成する。

【0042】

次に、コア1の巻芯部に、導線4を巻回する。具体的には、導線4の一方の端部4aをクランプ機構などに固定したうえで、ワイヤ供給ノズルなどを用いて巻回する。

【0043】

次に、導線4の両端部4a、4aを、絶縁被膜剥離剤に浸漬し、表面から絶縁被膜を剥離する。

【0044】

最後に、導線4の両端部4a、4aを、加圧冶具などにより加圧して、端子電極5、5に接続して、インダクタンス素子100を完成させる。なお、導線4の両端部4a、4aを端子電極5、5に接続する際には、加圧だけではなく、加熱したり、超音波振動を与えたりするようにしても良い。

【0045】

次に、第1実施形態にかかるインダクタンス素子100の実装状態について説明する。

【0046】

インダクタンス素子100は、端子電極5の主電極領域5aの幅が約1.0mmに形成されているため、図2(A)に示すように、幅1.0mmからなる幅狭ランド電極201、201に適切に実装することができる。(図2(A)においては、幅狭ランド電極201のインダクタンス素子100に隠れた部分を破線で示すとともに、インダクタンス素子100の底面に形成されているために見えない端子電極5をハッチング付きの破線で示している。以下、図2(B)において、同様の示し方をしている。)

また、インダクタンス素子100は、端子電極5の、一方の延長電極領域5bの端から他方の延長電極領域5bの端までの幅が約1.6mmに形成されているため、図2(A)に示すように、幅1.6mmからなる幅広ランド電極202、202にも、適切に実装することができる。

【0047】

このように、本発明の第1実施形態にかかるインダクタンス素子100は、幅の異なる、幅狭ランド電極201、201と幅広ランド電極202、202のいずれにも、良好に実装することができる。

【0048】

以上、本発明の第1実施形態にかかるインダクタンス素子100の構造と、製造方法の一例と、実装状態について説明した。しかしながら、本発明が上記の内容に限定されることはなく、発明の趣旨に沿って、種々の変形をなすことができる。

【0049】

たとえば、インダクタンス素子100においては、主電極領域5aの幅を約1.0mmとし、一方の延長電極領域5bの端から他方の延長電極領域5bの端までの幅を約1.6mmにしているが、幅寸法はこれらには限られず、実装するランド電極に合せて、適宜、変更することができる。

【0050】

[第2実施形態]

図3に、本発明の第2実施形態にかかるインダクタンス素子200を示す。

【0051】

インダクタンス素子200では、下鍔部13の底面13aに、導線4の両端部4a、4aを収容するための1対の溝13d、13dを設けた。インダクタンス素子200の他の構成は、図1(A)、(B)に示した、第1の実施形態にかかるインダクタンス素子100と同様にした。

【0052】

インダクタンス素子200においては、下鍔部13の底面13aに、導線の両端部4a、4aを収納するための溝13d、13dが形成されているため、導線の両端部4a、4aが、下鍔部13の底面13aから突出していない。したがって、インダクタンス素子200は、インダクタンス素子100よりも低背化されている。

【0053】

[第3実施形態]

図4に、本発明の第3実施形態にかかるインダクタンス素子300を示す。

【0054】

インダクタンス素子300では、各端子電極15の延長電極領域15bを、主電極領域15aから、下鍔部3の底面3aと側面3bが形成する辺にまで至るように形成した。インダクタンス素子300の他の構成は、図1(A)、(B)に示した、第1の実施形態にかかるインダクタンス素子100と同様にした。

【0055】

インダクタンス素子300においては、実装するランド電極に合せて定まる、一方の延長電極領域5bの端から他方の延長電極領域5bの端までの幅に、下側鍔部3の幅を合わせることができる。すなわち、インダクタンス素子300においては、下鍔部3の幅を、必要最小限にまで小さくし、小型化をはかることができる。

【0056】

[第4実施形態]

図5に、本発明の第4実施形態にかかるインダクタンス素子400を示す。

【0057】

インダクタンス素子400では、各端子電極25の主電極領域25aから、下鍔部3の側面3bに向かって、1対の延長電極領域25b、25bを、下鍔部3の端面3cに沿って形成した。インダクタンス素子300の他の構成は、図1(A)、(B)に示した、第1の実施形態にかかるインダクタンス素子100と同様にした。

【0058】

このように、各端子電極25における延長電極領域25bの形成位置は任意である。インダクタンス素子400も、幅の異なる2つのランド電極のいずれに対しても、良好に実装することができる。

【0059】

[第5実施形態]

図6に、本発明の第5実施形態にかかるインダクタンス素子500を示す。

【0060】

インダクタンス素子500では、各端子電極35の主電極領域35aから、下鍔部3の側面3bに向かって、それぞれ2対の延長電極領域35b、35bを形成した。すなわち、導線4の端部4aと端子電極35の接続部分の両側に、それぞれ、延長電極領域35b、35bを形成した。インダクタンス素子500の他の構成は、図1(A)、(B)に示した、第1の実施形態にかかるインダクタンス素子100と同様にした。

【0061】

このように、各端子電極35に設ける延長電極領域35b、35bの対数は任意であり、インダクタンス素子500も、幅の異なる2つのランド電極のいずれに対しても、良好に実装することができる。

【0062】

[第6実施形態]

図7に、本発明の第6実施形態にかかるインダクタンス素子600を示す。

【0063】

インダクタンス素子600では、各端子電極45の主電極領域45aから、下鍔部3の側面3bに向かって、途中に段部が形成され、異なる2つの長さを有する、1対の延長電極領域45bを形成した。すなわち、延長電極領域45bは、図7に示すように、主電極領域45aから下鍔部3の側面3bに向かって、異なる2つの長さL1と長さL2を備える。インダクタンス素子600の他の構成は、図1(A)、(B)に示した、第1の実施形態にかかるインダクタンス素子100と同様にした。

【0064】

このように、延長電極領域45bに段部を形成し、異なる2つの長さをもたせれば、主電極領域と延長領域とで、合計3つの異なる幅のランド電極のいずれにも実装することが可能になる。

【0065】

[第7実施形態]

図8に、本発明の第7実施形態にかかるインダクタンス素子700を示す。

【0066】

インダクタンス素子700では、各端子電極55の角部に丸みをもたせた。すなわち、各主電極領域55aおよび各延長電極領域55bは、それぞれ、角部に丸みを有している。インダクタンス素子700の他の構成は、図1(A)、(B)に示した、第1の実施形態にかかるインダクタンス素子100と同様にした。

【0067】

このように、端子電極の角部は直角である必要はなく、本実施形態の端子電極55のように、丸みを有していても良い。

【符号の説明】

【0068】

1:コア

2:上鍔部

3、13:下鍔部

3a、13a:底面

3b、13b:側面

3c、13c:端面

13d:溝

4:導線

4a:端部

5、15、25、35、45、55:端子電極

5a、15a、25a、35a、45a、55a:主電極領域

5b、15b、25b、35b、45b、55b:延長電極領域

5c:端面電極領域

【技術分野】

【0001】

本発明は、インダクタンス素子に関し、更に詳しくは、異なる複数の幅のランド電極のいずれにも実装可能なインダクタンス素子に関する。

【背景技術】

【0002】

各種電子機器に用いるインダクタンス素子として、ドラム型のコアに導線を巻回し、導線の両端部をコアに形成した端子電極に接続した構造からなるものが広く使用されている。

【0003】

たとえば、特許文献1(特開平2010‐171054号公報)に、そのような構造からなる従来のインダクタンス素子が開示されている。図9に、特許文献1に開示されたインダクタンス素子800を示す。

【0004】

インダクタンス素子800は、ドラム型のコア101を備える。コア101は、巻芯部(図示せず)の両端部に、上鍔部102、下鍔部103が形成された構造からなる。なお、図9においては、説明の都合上、インダクタンス素子800を上下逆に、すなわち、上鍔部102を下に、下鍔部103を上に示している。

【0005】

下鍔部103は、巻芯部側の内面(図示せず)と、底面103aと、1対の側面103bと、1対の端面103cを備えている。なお、側面103bは、複数の面が連なった形状からなる。

【0006】

また、コア101の巻芯部には、絶縁被覆が施された導線104が巻回されている。

【0007】

更に、コア101の下鍔部103の底面103aには、1対の端子電極105、105が形成されている。そして、導線104の両端部104a、104aが、それぞれ、下鍔部103の側面103bおよび底面103aを経由して、事前に絶縁被覆が剥離されたうえで、端子電極105、105に接続されている。

【0008】

なお、インダクタンス素子800においては、下鍔部103の底面103aに1対の溝103d、103dが形成され、溝103d、103dに導線104の両端部104a、104aが収容されている。また、端子電極105、105は、下鍔部103の底面103aに凹部(図示せず)を設け、その中にはんだを埋め込んだものからなる。しかしながら、溝103b、103bは必ずしも必要ではない。また、端子電極105、105は、凹部にはんだを埋め込んだものではなく、下鍔部103の底面103aに銀ペーストを焼付けるなどして形成したものの方が一般的である。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開平2010‐171054号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

しかしながら、上述した従来のインダクタンス素子800には、クリームはんだなどを使ったリフローはんだにより実装した場合に、特定の幅のランド電極には適切に実装できるが、それ以外の幅のランド電極には適切に実装できないという問題があった。

【0011】

すなわち、インダクタ素子に限らず、電子部品においては、その製造者や販売者(以下、「製造者等」という)により、推奨するランド電極の寸法が示される場合が多い。たとえば、製造者等であるA社では、図10(A)に示すように、幅1.0mm×長さ0.9mmの1対のランド電極(以下「幅狭ランド電極201」という)を、0.8mm間隔で対向させたものをランド電極として推奨し、それに合致した端子電極を備えたインダクタンス素子を製造、販売している。一方、別の製造者等であるB社では、図10(B)に示すように、幅1.6mm×長さ0.65mmの1対のランド電極(以下「幅広ランド電極202」という)を、0.7mm間隔で対向させたものをランド電極として推奨し、それに合致した端子電極を備えたインダクタンス素子を製造、販売している。

【0012】

なお、インダクタンス素子の実装は、基板などに形成された幅狭ランド電極201、201、または幅広ランド電極202、202の表面に、クリームはんだなどを塗布したうえで、インダクタンス素子を配置し、基板ごとトンネル炉などに入れて加熱し、続いてトンネル炉などから取出し冷却することによりおこなわれる。

【0013】

インダクタンス素子800は、端子電極105の幅が約1.0mmに形成されているため、図11(A)に示すように、幅狭ランド電極201、201には、適切に実装することができる。(図11(A)においては、幅狭ランド電極201のインダクタンス素子800に隠れた部分を破線で示すとともに、インダクタンス素子800の底面に形成されているために見えない端子電極105をハッチング付きの破線で示している。以下、図11(B)、図13(A)、(B)において、同様の示し方をしている。)

しかしながら、インダクタンス素子800を幅広ランド電極202、202に実装しようとすると、図11(B)に示すように、インダクタンス素子800が幅広ランド電極202、202上で回転してしまうことがあった。加熱してクリームはんだが溶融した際に、インダクタンス素子800の位置が安定せずに流動してしまったことによる。

【0014】

幅広ランド電極202、202にインダクタンス素子を適切に実装するためには、端子電極の幅を広く形成しなければならなかった。図12に、インダクタンス素子800の端子電極105の幅を広く設計変更した、別の従来のインダクタンス素子900を示す。

【0015】

インダクタンス素子900においては、端子電極115の幅が、約1.6mmに形成されている。インダクタンス素子900の他の構成は、上述したインダクタンス素子800と同じである。

【0016】

この結果、インダクタンス素子900は、図13(A)に示すように、幅広幅狭ランド電極201、201には、適切に実装することができる。

【0017】

しかしながら、インダクタンス素子900を幅狭ランド電極201、201に実装しようとすると、図13(B)に示すように、インダクタンス素子900が幅狭ランド電極201、201の片側にシフトしてしまうことがあった。加熱してクリームはんだが溶融した際に、インダクタンス素子900の位置が安定せずに流動してしまったことによる。

【0018】

このように、従来のインダクタンス素子800、900においては、クリームはんだなどを使ったリフローはんだにより実装した場合に、特定の幅のランド電極には適切に実装できるが、それ以外の幅のランド電極には適切に実装できないという問題があった。すなわち、A社とB社で推奨するランド電極の寸法が異なる場合、A社の推奨するランド電極にはA社のインダクタンス素子しか実装できず、B社の推奨するランド電極にはB社のインダクタンス素子しか実装できず、相互に互換性がないという問題があった。

【0019】

なお、端子電極115の幅を大きくした従来のインダクタンス素子900においては、導線104の断線を発見しにくいという別の問題もあった。すなわち、導線104の端部104aは、下鍔部103の側面103bを経由して、下鍔部103の底面103aに形成された端子電極115に接続されるが、導線104は、下鍔部103の側面103bと底面103aが形成する辺の近傍おいて断線しやすい。しかしながら、下鍔部103の底面103aにおいて、側面103bと底面103aが形成する辺の近傍に、幅を大きくした端子電極115が存在すると、目視による検査において、この部分における導線104の断線を見落としてしまいやすいという問題があった。すなわち、絶縁被覆が剥離された導線104と、端子電極115は、両者とも金属色であるため、導線104が断線しているにもかかわらず、断線していないように誤認してしまうことがあった。

【課題を解決するための手段】

【0020】

本発明は、上述した従来のインダクタンス素子の有する問題を解決するためになされたものであり、その手段として本発明のインダクタンス素子は、巻芯部と、その巻芯部の両端部に形成された上鍔部および下鍔部を備えたコアと、巻芯部に巻回された導線と、下鍔部に形成された1対の端子電極を備え、下鍔部は、内面と、底面と、1対の側面と、1対の端面を備え、1対の端子電極は、それぞれ下鍔部の底面に形成された主電極領域と、その主電極領域から下鍔部の1対の側面方向にそれぞれ延びた少なくとも1対の延長電極領域を備え、導線の両端部は、それぞれ下鍔部の側面および底面を経由して、端子電極に接続され、下鍔部の底面における導線の両端部が経由する領域には、端子電極の延長電極領域が形成されないようにした。

【0021】

なお、下鍔部の側面に、導線を経由させるための凹部を形成しても良い。この場合には、製造時や実装時などにおいて、下鍔部の側面に予期せず物体(装置、冶具、他の電子部品など)が衝突しても、導線が断線してしまうことがない。

【0022】

また、1対の端子電極は、それぞれ下鍔部の端面に、更に端面電極領域を備えるようにしても良い。この場合には、端面電極領域とランド電極の間にはんだフィレットを形成することができるため、強固な接合を実現することができる。

【0023】

また、端子電極の延長電極領域は、それぞれ途中に段部が形成され、主電極領域から下鍔部の側面に向かう方向に異なる複数の長さを備えるようにしても良い。たとえば、延長電極領域が異なる2つの長さを備える場合には、主電極領域と延長電極領域で、合計3つの異なる幅のランド電極のいずれにも実装することが可能になる。

【0024】

また、端子電極の延長電極領域は、それぞれ下鍔部の底面と側面が形成する辺にまで至って形成されるようにしても良い。

【発明の効果】

【0025】

本発明のインダクタンス素子は、主電極領域と、その主電極領域から、下鍔部の1対の側面方向にそれぞれ延びた少なくとも1対の延長電極領域を備えるようにしたため、複数の異なる幅のランド電極のいずれにも実装が可能になっている。

【0026】

また、本発明のインダクタンス素子は、下鍔部の底面の導線の両端部が経由する領域に、端子電極の延長電極領域を設けないようにしているため、この近傍で導線が断線した場合には、容易に発見することができる。

【図面の簡単な説明】

【0027】

【図1】図1(A)は、本発明の第1実施形態にかかるインダクタンス素子100を示す斜視図である。図1(B)は、インダクタンス素子100を示す底面図である。

【図2】図2(A)は、インダクタンス素子100を幅狭ランド電極201に実装した状態を示す平面図である。図2(B)は、インダクタンス素子100を幅広ランド電極202に実装した状態を示す平面図である。

【図3】本発明の第2実施形態にかかるインダクタンス素子200を示す底面図である。

【図4】本発明の第3実施形態にかかるインダクタンス素子300を示す底面図である。

【図5】本発明の第4実施形態にかかるインダクタンス素子400を示す底面図である。

【図6】本発明の第5実施形態にかかるインダクタンス素子500を示す底面図である。

【図7】本発明の第6実施形態にかかるインダクタンス素子600を示す底面図である。

【図8】本発明の第7実施形態にかかるインダクタンス素子700を示す底面図である。

【図9】従来のインダクタンス素子800を示す斜視図である。

【図10】図10(A)は、幅狭ランド電極201を示す平面図である。図10(B)は、幅広ランド電極202を示す平面図である。

【図11】図11(A)は、インダクタンス素子800を幅狭ランド電極201に実装した状態を示す平面図である。図11(B)は、インダクタンス素子700を幅広ランド電極202に実装した状態を示す平面図である。

【図12】別の従来のインダクタンス素子900を示す斜視図である。

【図13】図13(A)は、インダクタンス素子900を幅広ランド電極202に実装した状態を示す平面図である。図13(B)は、インダクタンス素子900を幅狭ランド電極201に実装した状態を示す平面図である。

【発明を実施するための形態】

【0028】

以下、図面とともに、本発明を実施するための形態について説明する。

【0029】

[第1実施形態]

図1(A)、(B)に、本発明の第1実施形態にかかるインダクタンス素子100を示す。ただし、図1(A)は斜視図、図1(B)は底面図である。

【0030】

インダクタンス素子100は、フェライトなどからなるドラム型のコア1を備える。コア1は、巻芯部(図示せず)の両端部に、上鍔部2、下鍔部3が形成された構造からなる。なお、図1(A)においては、説明の都合上、インダクタンス素子100を上下逆に、すなわち、上鍔部2を下に、下鍔部3を上に示している。コア1は、フェライトなどの磁性体で形成されていても良いし、アルミナなどの非磁性体で形成されていても良い。

【0031】

下鍔部3は、巻芯部側の内面(図示せず)と、内面の裏側の底面3aと、1対の側面3bと、1対の端面3cを備えている。なお、側面3bは、複数の面が連なった形状で構成されており、それらの面により、後述する導線4を経由させるための凹部3eが形成されている。

【0032】

また、コア1の巻芯部には、ポリウレタンなどの絶縁被覆が施された、Cu、Agなどからなる導線4が巻回されている。

【0033】

更に、コア1の下鍔部3の底面3aには、1対の端子電極5、5が形成されている。端子電極5、5は、たとえば、銀ペースト、銅ペーストなどを焼付けることにより形成されている。

【0034】

各端子電極5は、下鍔部3の底面3aに、主電極領域5aと、主電極領域5aから下鍔部3の1対の側面3b方向にそれぞれ延びた少なくとも1対の延長電極領域5b、5bを備える。更に、各端子電極5は、下鍔部3の端面3cに、端面電極領域5cを備える。なお、図1(B)においては、主電極領域5aと延長電極領域5bの間に破線を示しているが、これは説明のために示したものであり、実際には両者は一体的に形成されている。

【0035】

主電極領域5aは、図9(A)に示した、幅狭ランド電極201への実装を可能にする役割をはたすもので、約1.0mmの幅をもつ。一方、延長電極領域5b、5bは、図9(B)に示した、幅広ランド電極202への実装を可能にする役割をはたすもので、一方の延長電極領域5bの端から、他方の延長電極領域5bの端までは、約1.6mmの幅をもつ。そして、端面電極領域3cは、ランド電極との間にはんだフィレットを形成し、接合を強固にするとともに、実装位置を適正に調整するためのものである。

【0036】

そして、導線4の両端部4a、4aが、それぞれ、下鍔部3の側面3bおよび底面3aを経由して、事前に絶縁被覆が剥離されたうえで、端子電極5、5に接続されている。

【0037】

本発明においては、下鍔部3の底面3aにおける、導線4の端部4aと端子電極5の接続部分近傍に、端子電極5の延長電極領域5bが形成されておらず、下鍔部3の底面3aの素地がそのまま露出しているため、下鍔部3の側面3bと底面3aが形成する辺の近傍において導線4が断線しても、容易に断線を発見することができる。したがって、不良品が、良品と誤って出荷されてしまうようなことがない。

【0038】

なお、本実施形態においては、下鍔部3の側面3bが複数の面が連なった形状で構成され、それらの面により、側面3bに凹部3eが形成されている。したがって、凹部3eを経由させることにより、導線4の下鍔部3の側面3bにおける経由位置が安定している。

【0039】

かかる構造からなる、本発明の第1実施形態にかかるインダクタンス素子100は、たとえば、次の方法により製造される。

【0040】

まず、巻芯部の両端に上鍔部2と下鍔部3を備えた、ドラム型のコア1を作製する。具体的には、フェライト、アルミナなどの粉末を、所定の形状からなる金型に充填し、加圧して成形体を得る。続いて、その成形体を、所定のプロファイルで焼成して、コア1を得る。

【0041】

次に、コア1に、1対の端子電極5、5を形成する。具体的には、コア1の下鍔部3の底面3aおよび端面3cに、銀ペーストあるいは銅ペーストを所望の形状に印刷し、焼付けて形成する。

【0042】

次に、コア1の巻芯部に、導線4を巻回する。具体的には、導線4の一方の端部4aをクランプ機構などに固定したうえで、ワイヤ供給ノズルなどを用いて巻回する。

【0043】

次に、導線4の両端部4a、4aを、絶縁被膜剥離剤に浸漬し、表面から絶縁被膜を剥離する。

【0044】

最後に、導線4の両端部4a、4aを、加圧冶具などにより加圧して、端子電極5、5に接続して、インダクタンス素子100を完成させる。なお、導線4の両端部4a、4aを端子電極5、5に接続する際には、加圧だけではなく、加熱したり、超音波振動を与えたりするようにしても良い。

【0045】

次に、第1実施形態にかかるインダクタンス素子100の実装状態について説明する。

【0046】

インダクタンス素子100は、端子電極5の主電極領域5aの幅が約1.0mmに形成されているため、図2(A)に示すように、幅1.0mmからなる幅狭ランド電極201、201に適切に実装することができる。(図2(A)においては、幅狭ランド電極201のインダクタンス素子100に隠れた部分を破線で示すとともに、インダクタンス素子100の底面に形成されているために見えない端子電極5をハッチング付きの破線で示している。以下、図2(B)において、同様の示し方をしている。)

また、インダクタンス素子100は、端子電極5の、一方の延長電極領域5bの端から他方の延長電極領域5bの端までの幅が約1.6mmに形成されているため、図2(A)に示すように、幅1.6mmからなる幅広ランド電極202、202にも、適切に実装することができる。

【0047】

このように、本発明の第1実施形態にかかるインダクタンス素子100は、幅の異なる、幅狭ランド電極201、201と幅広ランド電極202、202のいずれにも、良好に実装することができる。

【0048】

以上、本発明の第1実施形態にかかるインダクタンス素子100の構造と、製造方法の一例と、実装状態について説明した。しかしながら、本発明が上記の内容に限定されることはなく、発明の趣旨に沿って、種々の変形をなすことができる。

【0049】

たとえば、インダクタンス素子100においては、主電極領域5aの幅を約1.0mmとし、一方の延長電極領域5bの端から他方の延長電極領域5bの端までの幅を約1.6mmにしているが、幅寸法はこれらには限られず、実装するランド電極に合せて、適宜、変更することができる。

【0050】

[第2実施形態]

図3に、本発明の第2実施形態にかかるインダクタンス素子200を示す。

【0051】

インダクタンス素子200では、下鍔部13の底面13aに、導線4の両端部4a、4aを収容するための1対の溝13d、13dを設けた。インダクタンス素子200の他の構成は、図1(A)、(B)に示した、第1の実施形態にかかるインダクタンス素子100と同様にした。

【0052】

インダクタンス素子200においては、下鍔部13の底面13aに、導線の両端部4a、4aを収納するための溝13d、13dが形成されているため、導線の両端部4a、4aが、下鍔部13の底面13aから突出していない。したがって、インダクタンス素子200は、インダクタンス素子100よりも低背化されている。

【0053】

[第3実施形態]

図4に、本発明の第3実施形態にかかるインダクタンス素子300を示す。

【0054】

インダクタンス素子300では、各端子電極15の延長電極領域15bを、主電極領域15aから、下鍔部3の底面3aと側面3bが形成する辺にまで至るように形成した。インダクタンス素子300の他の構成は、図1(A)、(B)に示した、第1の実施形態にかかるインダクタンス素子100と同様にした。

【0055】

インダクタンス素子300においては、実装するランド電極に合せて定まる、一方の延長電極領域5bの端から他方の延長電極領域5bの端までの幅に、下側鍔部3の幅を合わせることができる。すなわち、インダクタンス素子300においては、下鍔部3の幅を、必要最小限にまで小さくし、小型化をはかることができる。

【0056】

[第4実施形態]

図5に、本発明の第4実施形態にかかるインダクタンス素子400を示す。

【0057】

インダクタンス素子400では、各端子電極25の主電極領域25aから、下鍔部3の側面3bに向かって、1対の延長電極領域25b、25bを、下鍔部3の端面3cに沿って形成した。インダクタンス素子300の他の構成は、図1(A)、(B)に示した、第1の実施形態にかかるインダクタンス素子100と同様にした。

【0058】

このように、各端子電極25における延長電極領域25bの形成位置は任意である。インダクタンス素子400も、幅の異なる2つのランド電極のいずれに対しても、良好に実装することができる。

【0059】

[第5実施形態]

図6に、本発明の第5実施形態にかかるインダクタンス素子500を示す。

【0060】

インダクタンス素子500では、各端子電極35の主電極領域35aから、下鍔部3の側面3bに向かって、それぞれ2対の延長電極領域35b、35bを形成した。すなわち、導線4の端部4aと端子電極35の接続部分の両側に、それぞれ、延長電極領域35b、35bを形成した。インダクタンス素子500の他の構成は、図1(A)、(B)に示した、第1の実施形態にかかるインダクタンス素子100と同様にした。

【0061】

このように、各端子電極35に設ける延長電極領域35b、35bの対数は任意であり、インダクタンス素子500も、幅の異なる2つのランド電極のいずれに対しても、良好に実装することができる。

【0062】

[第6実施形態]

図7に、本発明の第6実施形態にかかるインダクタンス素子600を示す。

【0063】

インダクタンス素子600では、各端子電極45の主電極領域45aから、下鍔部3の側面3bに向かって、途中に段部が形成され、異なる2つの長さを有する、1対の延長電極領域45bを形成した。すなわち、延長電極領域45bは、図7に示すように、主電極領域45aから下鍔部3の側面3bに向かって、異なる2つの長さL1と長さL2を備える。インダクタンス素子600の他の構成は、図1(A)、(B)に示した、第1の実施形態にかかるインダクタンス素子100と同様にした。

【0064】

このように、延長電極領域45bに段部を形成し、異なる2つの長さをもたせれば、主電極領域と延長領域とで、合計3つの異なる幅のランド電極のいずれにも実装することが可能になる。

【0065】

[第7実施形態]

図8に、本発明の第7実施形態にかかるインダクタンス素子700を示す。

【0066】

インダクタンス素子700では、各端子電極55の角部に丸みをもたせた。すなわち、各主電極領域55aおよび各延長電極領域55bは、それぞれ、角部に丸みを有している。インダクタンス素子700の他の構成は、図1(A)、(B)に示した、第1の実施形態にかかるインダクタンス素子100と同様にした。

【0067】

このように、端子電極の角部は直角である必要はなく、本実施形態の端子電極55のように、丸みを有していても良い。

【符号の説明】

【0068】

1:コア

2:上鍔部

3、13:下鍔部

3a、13a:底面

3b、13b:側面

3c、13c:端面

13d:溝

4:導線

4a:端部

5、15、25、35、45、55:端子電極

5a、15a、25a、35a、45a、55a:主電極領域

5b、15b、25b、35b、45b、55b:延長電極領域

5c:端面電極領域

【特許請求の範囲】

【請求項1】

巻芯部と、当該巻芯部の両端部に形成された上鍔部および下鍔部を備えたコアと、

前記巻芯部に巻回された導線と、

前記下鍔部に形成された1対の端子電極を備えたインダクタンス素子であって、

前記下鍔部は、内面と、底面と、1対の側面と、1対の端面を備え、

前記1対の端子電極は、それぞれ前記下鍔部の前記底面に形成された主電極領域と、当該主電極領域から前記下鍔部の前記1対の側面方向にそれぞれ延びた少なくとも1対の延長電極領域を備え、

前記導線の両端部は、それぞれ前記下鍔部の前記側面および前記底面を経由して、前記端子電極に接続され、

前記下鍔部の前記底面における前記導線の両端部が経由する領域には、前記端子電極の前記延長電極領域が形成されていないインダクタンス素子。

【請求項2】

前記下鍔部の前記側面に、前記導線を経由させるための凹部が形成されている、請求項1に記載されたインダクタンス素子。

【請求項3】

前記1対の端子電極が、それぞれ前記下鍔部の前記端面に形成された、端面電極領域を更に備える、請求項1または2に記載されたインダクタンス素子。

【請求項4】

前記端子電極の前記延長電極領域は、それぞれ途中に段部が形成され、前記主電極領域から前記下鍔部の前記側面に向かって異なる複数の長さを備える、請求項1ないし3のいずれか1項に記載されたインダクタンス素子。

【請求項5】

前記端子電極の前記延長電極領域は、それぞれ前記下鍔部の前記底面と前記側面が形成する辺にまで至って形成されている、請求項1ないし4のいずれか1項に記載されたインダクタンス素子。

【請求項1】

巻芯部と、当該巻芯部の両端部に形成された上鍔部および下鍔部を備えたコアと、

前記巻芯部に巻回された導線と、

前記下鍔部に形成された1対の端子電極を備えたインダクタンス素子であって、

前記下鍔部は、内面と、底面と、1対の側面と、1対の端面を備え、

前記1対の端子電極は、それぞれ前記下鍔部の前記底面に形成された主電極領域と、当該主電極領域から前記下鍔部の前記1対の側面方向にそれぞれ延びた少なくとも1対の延長電極領域を備え、

前記導線の両端部は、それぞれ前記下鍔部の前記側面および前記底面を経由して、前記端子電極に接続され、

前記下鍔部の前記底面における前記導線の両端部が経由する領域には、前記端子電極の前記延長電極領域が形成されていないインダクタンス素子。

【請求項2】

前記下鍔部の前記側面に、前記導線を経由させるための凹部が形成されている、請求項1に記載されたインダクタンス素子。

【請求項3】

前記1対の端子電極が、それぞれ前記下鍔部の前記端面に形成された、端面電極領域を更に備える、請求項1または2に記載されたインダクタンス素子。

【請求項4】

前記端子電極の前記延長電極領域は、それぞれ途中に段部が形成され、前記主電極領域から前記下鍔部の前記側面に向かって異なる複数の長さを備える、請求項1ないし3のいずれか1項に記載されたインダクタンス素子。

【請求項5】

前記端子電極の前記延長電極領域は、それぞれ前記下鍔部の前記底面と前記側面が形成する辺にまで至って形成されている、請求項1ないし4のいずれか1項に記載されたインダクタンス素子。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2013−30673(P2013−30673A)

【公開日】平成25年2月7日(2013.2.7)

【国際特許分類】

【出願番号】特願2011−166897(P2011−166897)

【出願日】平成23年7月29日(2011.7.29)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

【公開日】平成25年2月7日(2013.2.7)

【国際特許分類】

【出願日】平成23年7月29日(2011.7.29)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

[ Back to top ]