セイコーインスツル株式会社により出願された特許

2,621 - 2,630 / 3,629

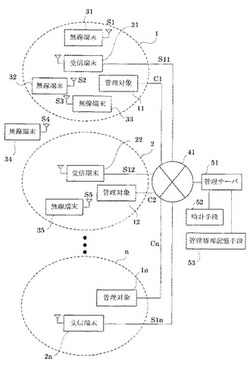

対象の数に合わせた最適制御システム、無線端末、制御機器

【課題】 室内の人数も加味して空調の制御を行う等、複数の対象の数に合わせた管理対象の最適な制御を行い得る最適制御システムを提供する。

【解決手段】 エリア1乃至nのそれぞれに配設した管理対象11乃至1nと、複数の検出対象のそれぞれに一対一に対応させて帰属させるとともにそれぞれが所定の端末信号を無線で送出する無線端末31乃至35と、エリア1乃至nのそれぞれに配設するとともに、端末信号を受信して受信した無線端末31乃至35の数を表す情報を少なくとも含む受信信号を送出する受信端末21乃至2nと、各受信信号を受信して処理し、各エリア1乃至n毎の無線端末31乃至35の数に基づく要素を少なくとも加味して各管理対象11乃至1nの所定の制御を行う管理サーバ51とを有する。

(もっと読む)

近視野光学ヘッド

【課題】 近視野光プローブを持つスライダーを使用して近視野光と記録媒体との相互作用によって、高密度な記録媒体に対して高速で信頼性の高い情報の記録および読取を実現させるための情報記録/読取装置を提供することを目的としている。

【解決手段】 近視野光プローブを持つスライダー1を記録媒体3に対して近接させ、さらに発光素子2と微小開口7との距離も短くし、圧電素子によって記録媒体3からの微小開口の突出量を制御することによって、プローブにおける光強度あるいは光検出部における光強度を上げ、記録媒体3との相互作用を増加する。このことにより高感度で正確な情報記録及び情報読取装置を実現する。

(もっと読む)

半導体装置、その製造方法、及び、表示装置の製造方法、

【課題】 30μm以下の電極ピッチを有する半導体素子を回路基板に電気的に接続することを可能にし、半導体素子の高密度実装を実現する。

【解決手段】 回路基板7にインターポーザ1をフェイスダウン接続し、半導体素子4をインターポーザ1へフェイスダウン接続することにより、半導体素子4は半導体配線間隔レベルで接続できるとともに、回路基板7には従来のピッチで接続することが可能となる。さらに、インターポーザに、機能回路が組み込まれた半導体基板を用いることにより、基板サイズが大幅に削減可能となり、製品の小型化に大きく貢献する。

(もっと読む)

カスコード回路および半導体装置

【課題】 低い電圧で動作する事が可能な、電源電圧変動除去比の高い基準電圧回路の提供。

【解決手段】 負荷回路の電源電圧供給端子に直列にデプレッショントランジスタ3を接続し、負荷回路に流れる電流を検知して電流源として動作するエンハンスメント型MOSトランジスタ4を接続し、該トランジスタに直列にデプレッション型MOSトランジスタ5を接続し、該トランジスタのゲート端子を該トランジスタのソース端子に接続した構成をとるバイアス回路を有し、デプレッション型トランジスタ3のゲート端子をデプレッション型トランジスタ5のソース端子に接続する構成とした。

(もっと読む)

サーマルプリンタ

【課題】 従来必須の構成品とされている専用の導通部品をなくした状態で静電気を確実に逃がすことができると共に、手間をかけずに効率良く製造でき、さらなる低コスト化を図ること。

【解決手段】 多数の発熱素子を有するサーマルヘッド11と、該サーマルヘッドを支持する導電性のヘッド支持体12と、記録紙を間に挟んだ状態でサーマルヘッドに対して周面が接触可能とされたプラテンローラと、筐体とヘッド支持体との間に設けられ、ヘッド支持体をプラテンローラに向けて付勢した状態で支持する導電性の付勢体15と、サーマルヘッドに電気的に接続されて信号を送るフレキシブル基板16とを備え、付勢体の一部15aが、フレキシブル基板に向けて延出していると共にフレキシブル基板に対して半田23により電気的に接続された状態で固定されてグランドが取られているサーマルプリンタを提供する。

(もっと読む)

半導体装置とその製造方法

【課題】アナログ半導体装置において、抵抗体は重要な素子として多用されている。抵抗体を多結晶シリコン膜で構成する場合、小さい面積で所望の抵抗値を得るために抵抗体の幅を最小にし、かつ薄膜化することが必要となる。抵抗体を薄膜化、かつコンタクト開口時の多結晶シリコン膜の突き抜けを防止した半導体装置を提供する。

【解決手段】多結晶シリコン膜で構成された高精度な抵抗体を有する半導体装置とその製造方法において、抵抗領域となる多結晶シリコン膜の下地絶縁膜の形状を凸形状とし、選択的に抵抗体となる多結晶シリコン膜を薄膜化し、電極引き出し領域は厚いままとすることで、コンタクトの突き抜けがなく高精度、高抵抗でかつ温度係数が良好である抵抗体を有する半導体装置とその製造方法を提供することが可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】 多層配線構造を有する半導体装置において、接続孔でクラウンを生じることが無く、高い長期信頼性を有し、生産性、経済性に優れ、十分低いViaホール抵抗を有する反射防止膜の形成方法を含む多層配線構造を有する半導体装置の製造方法を提供する。

【解決手段】 高融点金属膜と、SiあるいはSi化合物とからなる反射防止膜との積層膜を下層アルミニウム合金膜の上に配する。

(もっと読む)

力学量センサ

【課題】 配設される固定電極を有効に用いて、検出感度を向上させること。

【解決手段】 錘のx軸及びy軸方向の傾きを2軸検出回路において検出する。2軸検出回路は、x軸検出回路機能及びy軸検出回路機能を兼ね備え、x軸方向及びy軸方向の変位を検出する機能を兼有する固定電極からなる。2軸検出回路は、切替回路を介して回路内の結線を切り替えることにより、x軸検出回路機能及びy軸検出回路機能とを切り替える。2軸検出回路の結線状態の切り替えは、特定のクロック信号のタイミングに基づいて一定周期ごとに行われる。このように、固定電極を両回路機能において兼用することができるため、角速度の各軸方向の成分を固定電極の電極感度の総和に基づいて検出することができる。これにより、センササイズを増大させることなく、または、検出用の電極を増やすことなく検出感度を向上させることができる。

(もっと読む)

半導体装置

【課題】より簡単に素子間分離膜の端部におけるリーク電流の発生を抑制すること。

【解決手段】NMOSとPMOSとを電気的に分離するフィールド酸化膜を、LOCOS法を用いてSOI基板の活性層にシリコン酸化膜を成膜することにより形成する。フィールド酸化膜の端部には、酸化膜が薄くなるバーズビーク部が形成され、このバーズビーク部において寄生トランジスタが構成される。そのため、寄生トランジスタの作用で生じるリーク電流を抑制するためのチャネルカット領域を設ける。詳しくは、NMOSに、フィールド酸化膜のバーズビーク部であり、且つ、N+拡散層(ソース)におけるPウェル拡散層との2ヵ所の境界部にP+拡散領域を形成する。このようなチャネルカット領域を設けることにより、ゲートオフ時における寄生トランジスタにおける寄生チャネルによる電流パス(リーク電流)を抑制することができる。

(もっと読む)

バンドギャップ定電圧回路

【課題】 電源投入時の立ち上がり時間を速くし、通常状態でもノイズなどの影響で出力電圧が0Vで安定してしまうことを防ぐことが可能なバンドギャップ定電圧回路を提供する。

【解決手段】 出力端子の電圧をモニタする出力電圧検出回路と、出力電圧検出回路の出力によって電流値を制御される電流源を設け、出力端子の電圧が所定の電圧より低いときに、電流源によってレベルシフト回路を構成するバイポーラトランジスタに電流を供給するように構成した。

(もっと読む)

2,621 - 2,630 / 3,629

[ Back to top ]