シャープ株式会社により出願された特許

181 - 190 / 33,933

窒化物半導体発光素子および窒化物半導体発光素子の製造方法

【課題】活性層の内部量子効率を向上させた窒化物半導体発光素子および窒化物半導体発光素子の製造方法を提供する。

【解決手段】n型窒化物半導体層とp型窒化物半導体層との間に設けられたバッファ層および活性層と、を備え、バッファ層は、交互に積層された、Inx1Ga1-x1N(0<x1≦1)の式で表わされる第1のバッファ層と、Inx2Ga1-x2N(0≦x2<1、x2<x1)の式で表わされる第2のバッファ層と、を有しており、第1のバッファ層のIn組成x1は変化し、第1のバッファ層の少なくとも1層のIn組成x1が、活性層のIn組成よりも大きい窒化物半導体発光素子とその製造方法である。

(もっと読む)

光電変換素子およびその製造方法

【課題】高い変換効率を有する光電変換素子およびその製造方法を提供すること。

【解決手段】光電変換素子は、少なくとも1つの光電変換層を備える。この光電変換層は、p型微結晶半導体層、2層以上のi型半導体層、およびn型半導体層が順に積層されて構成されている。2層以上のi型半導体層のうちp型微結晶半導体層に接する第1のi型半導体層のバンドギャップエネルギーは、第1のi型半導体層以外のi型半導体層のバンドギャップエネルギーよりも大きい。

(もっと読む)

基板及びリード付き部品の半田付け方法

【課題】クリーム半田塗布領域を拡げずに実装強度を確保できるリード付き部品の実装方法を提供する。

【解決手段】基板1には、本体部110のリード(図示せず)を挿入するメッキ付きのリード挿入孔111及びリード挿入孔112を備え、リード挿入孔111の周囲にはクリーム半田塗布領域113が設けられ、リード挿入孔112の周囲にはクリーム半田塗布領域114が設けられている。リード挿入孔111に隣接してメッキ無しの半田補充孔115a、半田補充孔115b、及び半田補充孔115cが設けられ、リード挿入孔112に隣接してメッキ無しの半田補充孔116aが設けられている。半田補充孔115a、半田補充孔115b、及び半田補充孔115cの補充されたクリーム半田はリード挿入孔111に引き込まれ、半田補充孔116aの補充されたクリーム半田はリード挿入孔112に引き込まれることで、リード付き部品10が基板1に半田付けされる。

(もっと読む)

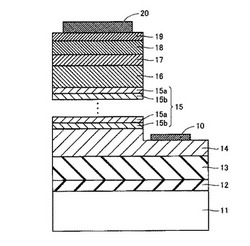

多接合型太陽電池

【課題】多接合型太陽電池におけるサブセルの短絡電流値を高め、よって、光電変換効率を向上させる。

【解決手段】基板を兼ねるボトムサブセル10と、複数のサブセルとを備える。複数のサブセルのうちの少なくとも1つは、基板10に格子整合されたp型半導体層21およびn型半導体層25と、p型半導体層21とn型半導体層25との間に挟まれ量子層23Aと障壁層23Bとが積層されて構成された超格子半導体層23とを有する。

(もっと読む)

光電変換素子および光電変換素子の製造方法

【課題】光劣化率を低減可能な光電変換素子を提供する。

【解決手段】光電変換素子10は、光電変換部3を備える。光電変換部3は、p型非晶質半導体層31、バッファ層32、i型非晶質半導体層33およびn型非晶質半導体層34を積層した構造からなる。バッファ層32における炭素原子の含有量は、基準値よりも少なく、基準値は、3×1014(個/cm2)〜1.2×1016(個/cm2)の範囲、または3×1014(個/cm2)〜1.4×1016(個/cm2)の範囲からなる。

(もっと読む)

光電変換素子および光電変換素子の製造方法

【課題】光劣化率を低減可能な光電変換素子を提供する。

【解決手段】光電変換素子10は、光電変換部3を備える。光電変換部3は、p型非晶質半導体層31、バッファ層32、シリコン薄膜33、i型非晶質半導体層34およびn型非晶質半導体層35を積層した構造からなる。バッファ層32は、1.98〜2.0eVの光学バンドギャップを有し、シリコン薄膜33は、1.88〜1.89eVの光学バンドギャップを有し、i型非晶質半導体層34は、1.85eVの光学バンドギャップを有する。その結果、バッファ層32とi型非晶質半導体層34との間のバンド不連続が小さくなる。また、i型非晶質半導体層34をプラズマCVD法によって形成するときに、p型非晶質半導体層31中のドーパント(ボロン)のi型非晶質半導体層34中への拡散が抑制される。

(もっと読む)

光電変換素子および光電変換素子の製造方法

【課題】光劣化率を低減可能な光電変換素子を提供する。

【解決手段】光電変換素子10は、光電変換部3を備える。光電変換部3は、p型非晶質半導体層31、バッファ層32、シリコン薄膜33、i型非晶質半導体層34およびn型非晶質半導体層35を積層した構造からなる。バッファ層32における炭素原子の含有量は、基準値よりも少なく、基準値は、3×1014(個/cm2)〜1.2×1016(個/cm2)の範囲、または3×1014(個/cm2)〜1.4×1016(個/cm2)の範囲からなる。また、シリコン薄膜33は、バッファ層32とi型非晶質半導体層34との間に配置され、バッファ層32の光学バンドギャップとi型非晶質半導体層34の光学バンドギャップとの間の光学バンドギャップを有する。

(もっと読む)

光電変換素子および光電変換素子の製造方法

【課題】裏面パッシベーション型の光電変換素子において、裏面電極のまわりに均質にBSFを形成し、変換効率を向上させる。

【解決手段】光電変換素子1は、片面にn型拡散層11が形成され、前記片面と反対側の面に凹部10bを有するp型結晶シリコン基板10と、前記p型結晶シリコン基板10の前記片面と反対側の面に接して形成され、前記凹部10bと対応する位置に開口部30bを有するパッシベーション膜30と、前記開口部30bを介して前記凹部10bと接するように形成されたアルミニウム電極43とを備え、前記p型結晶シリコン基板10は、該p型結晶シリコン基板10よりもドーパント濃度の高い高濃度p型拡散層13を前記凹部10bに有し、前記アルミニウム電極43は、前記p型結晶シリコン基板10の凹部10bに沿って窪んでいる。

(もっと読む)

光電変換素子および光電変換素子の製造方法

【課題】裏面パッシベーション型の光電変換素子において、裏面電極のまわりに均質にBSFを形成し、変換効率を向上させる。

【解決手段】光電変換素子1は、片面にn型拡散層11が形成され、前記片面と反対側の面に凹部10bを有するp型結晶シリコン基板10と、p型結晶シリコン基板10の前記片面と反対側の面に接して形成され、凹部10bと対応する位置に開口部30aを有するパッシベーション膜30と、開口部30aを介して凹部10bと接するように形成されたアルミニウム電極41とを備える。p型結晶シリコン基板10は、p型結晶シリコン基板10よりもドーパント濃度の高い高濃度p型拡散層12を凹部10bに有する。

(もっと読む)

光電変換素子

【課題】構造の自由度を確保して分極を抑制可能な光電変換素子を提供する。

【解決手段】光電変換素子100は、n型単結晶シリコン基板1と、n型非晶質膜2,21〜2mと、i型非晶質膜11〜1nと、p型非晶質膜31〜3m−1とを備える。n型単結晶シリコン基板1は、リン(P)が拡散された拡散領域10を含む。n型非晶質膜2は、n型a−Siからなり、n型単結晶シリコン基板1の光入射側の表面に接して形成される。i型非晶質膜11〜1nは、i型a−Siからなり、n型単結晶シリコン基板1の光入射側と反対側の表面に接して形成される。n型非晶質膜21〜2mは、n型a−Siからなり、それぞれ、i型非晶質膜11,13,・・・,1n−2,1nに接して形成される。p型非晶質膜31〜3m−1は、p型a−Siからなり、それぞれ、i型非晶質膜12,14,・・・,1n−1に接して形成される。

(もっと読む)

181 - 190 / 33,933

[ Back to top ]