ユニサンティス エレクトロニクス シンガポール プライベート リミテッドにより出願された特許

1 - 6 / 6

半導体装置

【課題】高集積なCMOS SRAMを提供する。

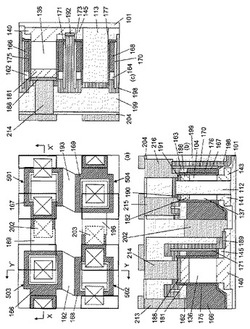

【解決手段】第1の第1導電型半導体137と、第1の第1導電型半導体とは極性が異なる第1の第2導電型半導体104と、第1の第1導電型半導体と第1の第2導電型半導体との間に配置される第1の絶縁物112が一体となり基板に対して垂直に延びる1本の第1の柱と、

第1の第1導電型半導体の上に配置される第1の第2導電型高濃度半導体182と、第1の第1導電型半導体の下に配置される第2の第2導電型高濃度半導体141と、第1の第2導電型半導体の上に配置される第1の第1導電型高濃度半導体186と、第1の第2導電型半導体の下に配置される第2の第1導電型高濃度半導体143と、第1の柱を取り囲む第1のゲート絶縁物176と、第1のゲート絶縁物を取り囲む第1のゲート導電体167と、を有するインバータ501を用いてSRAMを構成する。

(もっと読む)

半導体装置

【課題】1個の柱を用いてインバータを構成することにより、高集積なCMOSインバータ回路からなる半導体装置を提供する。

【解決手段】第1のシリコンと、該第1のシリコンとは極性が異なる第2のシリコンと、前記第1のシリコンと前記第2のシリコンとの間に配置され、基板に対して垂直方向に延びている第1の絶縁物とからなる1本の柱と、前記第1のシリコンの上下のそれぞれに配置され、前記第1のシリコンとは極性が異なる第1の高濃度不純物を含むシリコン層と、前記第2のシリコンの上下のそれぞれに配置され、前記第2のシリコンとは極性が異なる第2の高濃度不純物を含むシリコン層と、前記第1のシリコンと前記第2のシリコンと前記第1の絶縁物とを取り囲む第2の絶縁物と、前記第2の絶縁物を取り囲む導電体とを含む半導体装置により、上記課題を解決する。

(もっと読む)

固体撮像装置

【課題】ダイナミックレンジの拡大、高速シャッタ、低駆動電圧化を可能にする高画素密度な固体撮像装置を提供する。

【解決手段】画素1aは、第2の半導体領域3を共有する少なくとも4つの第1〜第4半導体層5a〜5dを備えている。第1の半導体層5aは、第1の外部回路と電気的に接続された第1の半導体領域2と、第2の半導体領域3によって第1の半導体領域から分離されるとともに、第2の外部回路と電気的に接続された第3の半導体領域4とを有する。第2の半導体層5bには、絶縁膜6a、6bと、第3の外部回路と電気的に接続されたゲート導体電極7a、7bとを有するMOSトランジスタが形成されている。第3の半導体層5cは、第2及び第4の半導体領域3、8a、8bからなるフォトダイオードを有する。第4の半導体領域がゲート、第1の半導体領域及び前記第5の半導体領域の内の一方がドレイン、他方がソースとなる接合トランジスタが形成されている。

(もっと読む)

不揮発性半導体メモリトランジスタ、および、不揮発性半導体メモリの製造方法

【課題】浮遊・制御ゲート間の容量を増大できる、島状半導体を用いた不揮発性半導体メモリトランジスタを提供する。

【解決手段】不揮発性半導体メモリトランジスタは、Si基板側からソース領域303、チャネル領域304及びドレイン領域302がこの順に形成された島状半導体301と、前記チャネル領域の外周を囲むように、トンネル絶縁膜305を間に介在させて配置された浮遊ゲート306と、浮遊ゲートの外周を囲むように、インターポリ絶縁膜307を間に介在させて配置された制御ゲート308aと、制御ゲートに接続され、所定方向に延びる制御ゲート線308と、を備える。浮遊ゲートは制御ゲートの下方及び上方領域、並びに、制御ゲート線の下方領域まで夫々延在され、浮遊ゲートと、制御ゲートの上面、下面及び内側面との間、及び、浮遊ゲートの、制御ゲート線の下方領域まで延在した部分と、制御ゲート線との間には、夫々インターポリ絶縁膜が介在配置される。

(もっと読む)

半導体装置及びその製造方法

【課題】良好な特性を有しながら、半導体製造工程における半導体製造装置と半導体装置とへの金属汚染を抑制するような構造を有する半導体装置、および、その製造方法を提供する。

【解決手段】本発明の半導体装置は、nMOS SGT220であり、第1の平面状シリコン層上234に垂直に配置された第1の柱状シリコン層232表面に並んで配置された、第1のn+型シリコン層113と、金属を含む第1のゲート電極236と、第2のn+型シリコン層157とから構成される。そして、第1の絶縁膜129が、第1のゲート電極236と第1の平面状シリコン層234との間に、第2の絶縁膜162が第1のゲート電極236の上面に配置されている。また、金属を含む第1のゲート電極236が、第1のn+型シリコン層113、第2のn+型シリコン層157、第1の絶縁膜129、および、第2の絶縁膜162に囲まれている。

(もっと読む)

不揮発性半導体メモリトランジスタ、不揮発性半導体メモリ、および、不揮発性半導体メモリの製造方法

【課題】浮遊ゲートと制御ゲート間の容量を大きくすることができるとともに、かつ制御ゲートと島状半導体間の寄生容量を低減する、島状半導体を用いた構造を持つ不揮発性半導体メモリ、およびその製造方法を提供する。

【解決手段】不揮発性半導体メモリを構成する不揮発性半導体メモリトランジスタは、基板側からソース領域303、チャネル領域304及びドレイン領域302がこの順に形成された島状半導体301と、チャネル領域の外周を囲むように、トンネル絶縁膜305を間に介在させて配置された中空柱状の浮遊ゲート306と、当該浮遊ゲートの外周を囲むように、インターポリ絶縁膜307を間に介在させて配置された中空柱状の制御ゲート308と、を備えている。浮遊ゲートと、制御ゲートの上面、下面および内側面との間には、インターポリ絶縁膜が介在配置されている。

(もっと読む)

1 - 6 / 6

[ Back to top ]