ラピスセミコンダクタ宮崎株式会社により出願された特許

1 - 10 / 151

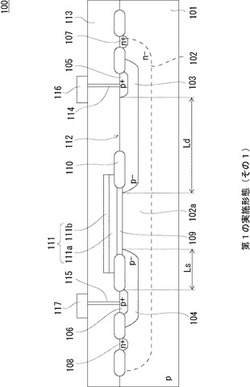

高耐圧電界効果トランジスタ

【課題】高耐圧電界効果トランジスタの素子面積を増大させること無しに、十分に低いオン抵抗を得る。

【解決手段】半導体基板101のn型領域102内に、チャネル形成領域102aを挟んでドレイン低濃度領域103およびソース低濃度領域104を形成し、ドレイン高濃度領域105およびソース高濃度領域106を形成し、ゲート酸化膜109を形成し、該ゲート酸化膜109の端部および低濃度領域103,104を含む領域にフィールド酸化膜110を形成し、さらにゲート酸化膜109からフィールド酸化膜110の端部にかけてゲート電極111を形成した高耐圧pMOSトランジスタにおいて、ゲート電極111とドレイン高濃度領域105との間に、フィールド酸化膜110が形成されていない非酸化領域112を設ける。製造時に、ドレイン低濃度領域103の不純物がフィールド酸化膜110に取り込まれ難くなるので、オン抵抗の増加が抑制される。

(もっと読む)

リードフレーム

【課題】半導体装置の大型化を防止する構造体を提供する。

【解決手段】リードフレーム20は、基板搭載領域24aaが設けられている第1主面24a及び第1主面に対向しており、ダイパッド側半導体チップ搭載領域25が設けられている第2主面24bを有していて、基板搭載領域内であってかつダイパッド側半導体チップ搭載領域外に、主面間を貫通して設けられている1つ又は2つ以上の開口部26を有するダイパッド24を有している。ダイパッドの開口部から複数の半導体チップ接続用第2電極パッド34を露出させてダイパッドに搭載される基板30と、ダイパッド及び基板に搭載される複数の半導体チップ40と、半導体チップ40のチップ電極パッド42と基板の半導体チップ接続用第1及び第2電極パッド32及び34とを接続するボンディングワイヤ50と、これらを覆い、かつリード28の一部分を露出させて設けられる封止部60とを含んでいる。

(もっと読む)

半導体装置

【課題】他のパッケージとの接続信頼性及び耐湿信頼性に優れた構造の両面電極パッケージを、簡易且つ低コストに製造できるようにする。また、半導体チップのピンの数や大きさに応じて、任意のレイアウトで内部配線(電極パッド)を形成できる構造の両面電極パッケージを、簡易且つ低コストに製造できるようにする。

【解決手段】電極パッド18、配線20、貫通電極28、ランド30、及びソルダレジスト42が形成されたコア材16に、銅箔を貼り付ける。この銅箔を数段階にわたってウエットエッチングすることで、配線20上に略垂直に立てられ、側面に周方向に沿って全周にわたり形成された複数の突条(周方向に連続した凸部)を備えた表面側端子36を形成する。表面側端子36の周囲を封止樹脂で封止し、封止樹脂層50から表面側端子36の端面36Aを露出させて、封止樹脂層50の表面で再配線を行う。

(もっと読む)

半導体装置

【課題】パッケージへ伝達された熱や応力に対して安定した動作が可能な半導体装置を提供する。

【解決手段】半導体加速度センサ装置1は、内部にキャビティ21cを有するパッケージ21と、所定の素子を有する半導体チップ10と、上面の所定領域32aに半導体チップが固着されたスペーサ32と、スペーサ32の下面における所定領域32a下以外の領域とキャビティ内のパッケージの底面21aとを接着する接着部33とを備え、半導体チップに形成された第1電極パッド16と、パッケージに形成され、少なくとも一部がキャビティ内部で露出された配線パターン23と、パッケージの底面に形成され、配線パターンと電気的に接続された第2電極パッド22と、第1電極パッドと、露出された配線パターンとを接続する金属ワイヤ26とをさらに有する。

(もっと読む)

半導体装置

【課題】半導体チップの小型化に適応すると共に、リードフレームやBGA基板に半導体チップを搭載した半導体装置の更なる薄型化を図る手段を提供する。

【解決手段】半導体装置が、半導体チップと、半導体チップのチップおもて面に形成された複数のチップ電極と、半導体チップの外側に位置するリード部を有する複数のリード端子と、チップおもて面と一定の距離を保ってチップおもて面の外側へ延在し、チップ電極とリード端子とを接続する複数の導電性配線であって、チップおもて面の第1辺を横切って、一のチップ電極と一のリード端子とに亘って延在し、第1辺の外側で屈曲する第1導電性配線と、第1辺とは異なる第2辺を横切って、他のチップ電極と他のリード端子とに亘って延在する第2導電性配線とを含む当該複数の導電性配線と、を備え、第2導電性配線が接続されるリード端子は、第1導電性配線が接続するリード端子と形状が異なる。

(もっと読む)

洗浄方法

【課題】 レジストフィルタ部の内容積を低減して容易にして、確実で、しかも安全なレジスト配管の洗浄が可能な洗浄方法を提供する。

【解決手段】 配管を有するレジスト塗布装置を洗浄する方法において、前記配管に接続され、上面及び下面によって画成される流路とこの流路内に配置されるフィルタとを有する治具を用いてレジストを供給する工程と、前記治具に代えて、前記治具の上面と下面との幅よりも狭い上面及び下面により画成される流路を有し、この流路にはフィルタを配置しない治具を用いて洗浄する工程と、を有する。

(もっと読む)

半導体製造方法

【課題】複数のウェハをボートに乗せて熱処理を行う際に生じるウェハの反りによるウェハ間の接触傷等を防止する。

【解決手段】半導体製造方法は、複数枚のウェハ60が乗せられたボート50を熱処理炉40内へ導入して、それらのウェハ60を加熱する加熱工程と、熱処理炉40からボート60を導出し、センサ43,44により、複数枚のウェハ60の反り方向を検出する反り方向検出工程と、反り方向が同一のウェハ60を分別し、反り方向が同一のウェハ60を別々のボートへ再収容する分別処理工程と、反り方向が同一のウェハ60が収容されたボートを熱処理炉40へ導入して、所定温度で熱処理を行う熱処理工程とを有している。

(もっと読む)

半導体装置の製造装置

【課題】簡素な構造で、半導体基板のおもて面側へのエッチング液の巻き込みを抑制する手段を提供する。

【解決手段】 半導体基板を、噴出口から半導体基板の半径方向外側に向けて噴出させた噴出ガスにより非接触で保持する回転基台と、回転基台に設けられ、半導体基板の外周面に接触する複数の位置決めピンとを備えた半導体装置の製造装置において、位置決めピンの外周面に、噴出ガスの流れを半径方向外側に案内する案内溝を設ける。

(もっと読む)

EEPROMの製造方法

【課題】高い不純物濃度を有する拡散領域によってメモリセルトランジスタと選択トランジスタとが確実に接続されるEEPROMの製造方法を提供する。

【解決手段】半導体基板にメモリセルトランジスタのソース及びドレイン領域を形成し、半導体基板上にメモリセルトランジスタ及び選択トランジスタのゲート電極構造を形成した後に、メモリセルトランジスタのドレイン領域と部分的に重ねて選択トランジスタのソース領域を形成する。

(もっと読む)

センサ装置

【課題】良好な耐衝撃性を有し、小型化が可能なセンサ装置を提供する。

【解決手段】支持部24の枠部10上面と対向する面36、枠部10の支持部24底面と対向する面38、及び第1絶縁層14の錘部12側の側面20により区画された第1凹部30と、質量部26の錘部12上面と対向する面40、錘部12の質量部26底面と対向する面42、及び第2絶縁層18の枠部10側の側面22により区画された第2凹部32と、梁部16の支持部24と質量部26との接続方向上に位置する第1絶縁層14の錘部12側の側面又は第2絶縁層18の枠部10側の側面に形成された第3凹部70と、を有し、第1凹部30の深さ34及び第2凹部32の深さ35が枠部10の幅の3.3%以上5.0%以下である。

(もっと読む)

1 - 10 / 151

[ Back to top ]