株式会社ゼネラル リサーチ オブ エレクトロニックスにより出願された特許

1 - 10 / 32

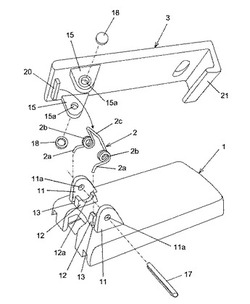

クリップ装置

【課題】ベース部材、開閉部材、及びダブルトーションばねを連結する作業工程を少なくすることができるクリップ装置の提供。

【解決手段】ベース部材1と開閉部材3が両方の軸受部11,15と支軸17を介して連結され、ベース部材1と開閉部材3との間に設けられたダブルトーションばね2により挟持部21が離間して付勢するクリップ装置において、ベース部材1は、ダブルトーションばね2を軸受部11間で圧縮保持する一対の軸受部11と、ダブルトーションばね2の巻回部2bの軸芯方向に直交する方向のうちベース部材1に平行する方向に対してダブルトーションばね2を位置決めする位置決め片12と、軸受部11と位置決め片12との間に穿設され、ダブルトーションばね2の先端を挿入する穴13とを有する。

(もっと読む)

信号品質検知システム

【課題】ディジタル伝送信号の基準伝送速度時及び基準伝送速度の2分の1の時の各ビットエラーの発生頻度を同時検出する信号品質検知システムを提供する。

【解決手段】送信側は単位ビット列の各ビットを連続した2ビットにしてパリティチェック用ビット列を送信し、受信側は基準伝送速度時のビットエラー判定回路及び基準伝送速度の2分の1の時のビットエラー判定回路とからなるパリティチェック用ビット列品質検知回路を備え、基準伝送速度時のビットエラー判定回路は、受信パリティチェック用ビット列の連続した2ビット中の1ビットを検出し、検出した各ビットを用いて基準伝送速度時のパリティチェック用ビット列を形成し、基準伝送速度の2分の1の時のビットエラー判定回路は、受信パリティチェック用ビット列の対応して連続供給された2ビットを加算し、この加算ビットを用いて基準伝送速度の2分の1の時のパリティチェック用ビット列を形成する。

(もっと読む)

受信機入力回路

【課題】アンテナ輻射回路と周波数選択回路4間に半導体バッファ回路3を配置することにより、インピーダンス整合調整を行わずに良好なSN比を得ることができる受信機入力回路を提供する。

【解決手段】アンテナ給電線7が接続されるアンテナ入力端子1と、アンテナ入力端子1に結合コンデンサ2を通して入力端が接続されるエミッタフォロワトランジスタ回路3と、エミッタフォロワトランジスタ路3の出力端に結合される周波数選択回路4と、周波数選択回路4の周波数選択出力信号が供給される高周波増幅段5とを備え、アンテナ入力端子1にアンテナ6に誘起された受信信号波長に比べて極めて短いアンテナ給電線7が接続され、半導体バッファ回路3によりアンテナ輻射回路と周波数選択回路4との電気的結合を隔離した。

(もっと読む)

可変容量回路

【課題】可変容量ダイオード2への印加逆制御電圧変化対その容量変化の関係を線形にする補正手段に負性インピーダンス変換回路3を用い、容量変化範囲を狭くせず、複雑な補正手段を用いずに済む可変容量回路を提供する。

【解決手段】非接地側入力端子1aと接地側入力端子1b間に接続され、可制御電圧形成装置6の可変制御電圧が供給される可変容量ダイオード2と、入力端と出力端と接地端を有し、入力端が記非接地側入力端子1aに、出力端が容量素子5を介して接地側入力端子1bに接続された負性インピーダンス変換回路3を備え、容量素子5の容量を非接地側入力端子1aと接地側入力端子1b間に形成される分布容量に略等しい値に選び、可制御電圧形成装置6の調整によって可変制御電圧を線形変化させるに伴い可変容量ダイオード2の容量を対数的に変化させるように形成した。

(もっと読む)

受信機入力回路

【課題】周波数選択回路1と高周波入力段3間に2端子型浮動負性抵抗回路2を接続し、その負性抵抗により周波数選択回路1に形成される抵抗成分を打ち消すことにより受信機入力回路における雑音指数を大幅に低減できる受信機入力回路を提供する。

【解決手段】受信した高周波信号を選択する周波数選択回路1と、周波数選択回路1で選択した高周波信号を供給する高周波入力段3とを備える受信機入力回路において、周波数選択回路1と高周波入力段3間に2端子型浮動負性抵抗回路2を接続し、2端子型浮動負性抵抗回路2の負性抵抗により周波数選択回路1に形成される抵抗成分を打ち消すようにした。

(もっと読む)

浮動アクティブインダクタ

【課題】回路構成を複雑にすることなしに、そのインダクタンス値及びその内部抵抗値を個別に設定することが可能な浮動アクティブインダクタを提供する。

【解決手段】第1及び第2入力端子1、2間に直列接続された浮動インダクタ回路A及び浮動負性抵抗回路Bと、それらの回路A、Bの直列接続点3を備え、第1及び第2入力端子1、2間に浮動アクティブインダクタが形成されるもので、浮動インダクタ回路Aは、第1入力端子1と直列接続点3間に直列接続された第1キャパシタ4、第1抵抗5、第2キャパシタ6と、第1キャパシタ4の両端に第1低抵抗8を介して接続された第1電圧フォロワ8と、第2キャパシタ6の両端に第2低抵抗を介して接続された第2電圧フォロワ8からなり、浮動負性抵抗回路Bは、直列接続点3と第2入力端子2間に直列接続された第2乃至第6抵抗11〜15と、第2及び第3抵抗11、12に接続された第1オペアンプ16と、第5及び第6抵抗14、15に接続された第2オペアンプ17からなる。

(もっと読む)

浮動アクティブリアクタ

【課題】用いるオペアンプ数が少なく、内部回路構成を大幅に簡素化した浮動アクティブリアクタを提供する。

【解決手段】 第1及び第2入力端子1、2間に接続された第1乃至第4インピーダンス素子3(1)〜3(4)の直列回路3、第1及び第2電圧フォロワ4、5、それらの出力端に直列接続した低抵抗値の抵抗素子6、7で構成され、直列回路3は両側に配置の第1及び第4インピーダンス素子3(1)、3(4)と中間に配置の第2及び第3インピーダンス素子3(2)、3(3)のいずれか一方を等低抵抗値の抵抗素子に、他方を同種の素子で等リアクタンス値のリアクタ素子にし、第1電圧フォロワ5は入力端を第1移相信号出力端bに、出力端を抵抗素子6を通して第1入力端子1に接続し、第2電圧フォロワ6は入力端を第2移相信号出力端cに、出力端を抵抗素子7を通して第2入力端子2に接続し、第1、第2入力端子1、2間に信号電圧を供給すると第1、第2入力端子1、2間に浮動アクティブリアクタが形成される。

(もっと読む)

浮動アクティブリアクタ

【課題】既知の浮動アクティブリアクタに比べ用いるオペアンプの数が少なく、内部の回路構成を極限まで簡素化した浮動アクティブリアクタを提供する。

【解決手段】第1及び第2入力端子1、2、インピーダンス3(1)〜3(4)をブリッジ接続したブリッジ回路3、電圧フォロワ4、5、低抵抗値の第1及び第2抵抗6、7からなり、ブリッジ回路3の入力端a、cを各別に第1及び第2入力端子1、2に、ブリッジ回路3の出力端b、dを各別に電圧4、5の入力端に、電圧フォロワ4、5の出力端を各別に第1及び第2抵抗6、7を通して第1及び第2入力端子1、2に接続した構成を有し、ブリッジ回路3の相対する一辺に配置するインピーダンスを同種のリアクタ素子で等リアクタンス値の素子に、相対する他辺に配置するインピーダンスを抵抗素子で等抵抗値の素子に選び、第1及び第2入力端子1、2に信号電圧の供給時、第1及び第2入力端子1、2間に浮動アクティブリアクタが形成される。

(もっと読む)

浮動アクティブインダクタ

【課題】既知のものに比べ用いるオペアンプ数が少なく、簡素化された回路構成であり、内部の回路構成をより簡素化した浮動アクティブインダクタを提供する。

【解決手段】 第1及び第2入力端子1、2間に接続された4素子ブリッジ回路型の1次のパッシブ全域通過形進相回路3、当該パッシブ全域通過形進相回路3の出力進相信号を単位利得増幅する電圧フォロワ4、電圧フォロワ4の出力進相信号を反転増幅する位相反転回路5、電圧フォロワ4の出力と第1入力端子1間に接続した低抵抗値の第1抵抗6、位相反転回路5の出力と第2入力端子2間に接続した低抵抗値の第2抵抗7を備え、ブリッジ回路は、2素子が第1及び第2入力端子1、2間に直列接続した等高抵抗値を有する2つの抵抗3(1)、3(2)で、2素子が第1及び第2入力端子1、2間に直列接続したキャパシタ3(3)と抵抗3(4)であり、当該キャパシタ3(3)と抵抗3(4)の接続点から進相信号を得ている。

(もっと読む)

浮動アクティブキャパシタ

【課題】既知のものに比べ用いるオペアンプ数が少なく、簡素化された回路構成であり、内部の回路構成をより簡素化した浮動アクティブキャパシタを提供する。

【解決手段】 第1及び第2入力端子1、2間に接続された4素子ブリッジ回路型の1次のパッシブ全域通過形遅相回路3、当該パッシブ全域通過形遅相回路3の出力遅相信号を単位利得増幅する電圧フォロワ4、電圧フォロワ4の出力遅相信号を反転増幅する位相反転回路5、電圧フォロワ4の出力と第1入力端子1間に接続した低抵抗値の第1抵抗6、位相反転回路5の出力と第2入力端子2間に接続した低抵抗値の第2抵抗7を備え、ブリッジ回路は、2素子が第1及び第2入力端子1、2間に直列接続した等高抵抗値を有する2つの抵抗3(1)、3(2)で、2素子が第1及び第2入力端子1、2間に直列接続した抵抗3(3)とキャパシタ3(4)であり、当該抵抗3(3)とキャパシタ3(4)の接続点から遅相信号を得ている。

(もっと読む)

1 - 10 / 32

[ Back to top ]