マクロニクス インターナショナル カンパニー リミテッドにより出願された特許

1 - 10 / 13

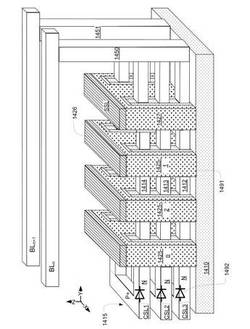

メモリストリングにダイオードを有する3次元アレイのメモリアーキテクチャ

【課題】信頼でき、非常に小型の3次元集積回路メモリ用の構造を低い製造コストで提供する。

【解決手段】3次元アレイは第1の端部と第2の端部を含む2つの端部を有し、第1の端部と第2の端部の一方はビット線BLに接続され、第1の端部と第2の端部の他方はソース線CSLに接続される不揮発性メモリセルのNANDストリングのスタック1412、1413、1414と、ビット線BL及びソース線SLの一方をメモリセルのストリング1412、1413、1414に接続させるダイオード1492を有する。

(もっと読む)

ダイオードストラッピングを備えた熱アシストフラッシュメモリ

【課題】フラッシュメモリの動作速度及び耐久性を向上させる技術の提供。

【解決手段】メモリが、行及び列を含むメモリセルのアレイを有している。該メモリは、アレイ内の単数又は複数のワード線上の第1の離隔位置のセットに第1のバイアス電圧を印加するとともに、単数又は複数のワード線上の第2の離隔位置のセットに第1のバイアス電圧とは異なる第2のバイアス電圧を印加する、ワード線に結合された回路部を有し、第1の離隔位置のセットにおける位置は、第2の離隔位置のセットの位置の間に介在しており、それにより、第1の離隔位置のセットにおける位置と第2の離隔位置のセットにおける位置との間に、単数又は複数のワード線の加熱をもたらす電流の流れが誘導される。

(もっと読む)

積層した接続レベルを有する集積回路装置用マスク数の低減法

【課題】3D積層メモリ装置は、各接続レベル毎に別個のマスクが使用されるので必要なマスク数は多くなるが、パターンを工夫して必要マスク数を減らす。

【解決手段】3次元積層集積回路装置は配線領域に接続レベルの積層部を有する。接続レベルの積層部で2のN乗個のレベルまで含む配線接続領域を形成するためのN個のエッチングマスクの組だけが必要とされる。幾つかの例によれば、2のX−1乗(2X−1)個の接続レベルは、連続番号Xのエッチングマスクでエッチングされ、1つのマスクがX=1であり、他の1つのマスクがX=2であり、X=Nまで付与される。当該方法は接続レベルでの形成領域に整合した配線接続領域を形成する。

(もっと読む)

不揮発性メモリセル、これを有するメモリアレイ、並びに、セル及びアレイの操作方法

【課題】向上されたデータ保持性能及び向上された動作速度をもって、多数回にわたり動作(プログラム/消去/読み出し)させることのできる不揮発性メモリセル設計及びアレイを提供する。

【解決手段】半導体基板101であって、該基板101の表面より下に配置され且つチャネル領域106によって分離されたソース領域102及びドレイン領域104を備えた半導体基板101と前記チャネル領域106より上に配置されたトンネル誘電体構造120であって、低いホールトンネリング障壁高さを有する少なくとも1つの層を備えたトンネル誘電体構造120と前記トンネル誘電体構造120より上に配置された電荷蓄積層130と前記電荷蓄積層130より上に配置された絶縁層140と前記絶縁層140より上に配置されたゲート電極150とを有するメモリセル100を、該メモリセル100のアレイ及び操作方法と共に開示する。

(もっと読む)

不揮発性メモリセル、これを有するメモリアレイ、並びに、セル及びアレイの操作方法

【課題】自己収束消去動作を容易にすると共に保持状態の期間におけるメモリデバイスの電荷蓄積層内での電荷保持能力を保持してもいるトンネル誘電体構造を有する不揮発性メモリデバイスの提供。

【解決手段】半導体基板101であって、該基板の表面より下に配置され且つチャネル領域106によって分離されたソース領域102及びドレイン領域104を備えた半導体基板と、前記チャネル領域より上に配置されたトンネル誘電体構造102であって、低いホールトンネリング障壁高さを有する少なくとも1つの層を備えたトンネル誘電体構造と、前記トンネル誘電体構造より上に配置された電荷蓄積層130と、前記電荷蓄積層より上に配置された絶縁層140と、前記絶縁層より上に配置されたゲート電極150とを有するメモリセル、該メモリセルのアレイ及び操作方法と共に開示する。

(もっと読む)

高速消去式電荷捕捉メモリーセル

【課題】 7Vほどものメモリーウィンドウを有する高速なプログラムと消去の速度を達成する。

【解決手段】 バンドギャップを構造設計した電荷捕捉メモリーセルは、プラチナゲートのような金属又は金属化合物のゲートから、酸化アルミニウムのような高い誘電定数を有する材料のブロッキング層によって隔離され、チャンネルを含む半導体本体から改良されたトンネリング誘電体によって隔離される電荷捕捉素子を有する。

(もっと読む)

不揮発性メモリセル、これを有するメモリアレイ、並びに、セル及びアレイの操作方法

【課題】自己収束消去動作を容易にすると共に電荷保持能力を有する不揮発性メモリデバイスの提供。

【解決手段】半導体基板であって、該基板の表面より下に配置され且つチャネル領域106によって分離されたソース領域102及びドレイン領域104を備えた半導体基板と101;前記チャネル領域106より上に配置されたトンネル誘電体構造であって、低いホールトンネリング障壁高さを有する少なくとも1つの層を備えたトンネル誘電体構造120と;前記トンネル誘電体構造より上に配置された電荷蓄積層130と;前記電荷蓄積層より上に配置された絶縁層140と;前記絶縁層より上に配置されたゲート電極150と;を有するメモリセル。

(もっと読む)

フラッシュメモリのリフレッシュ方法

【課題】複雑なプロセスを増やしていない回路設計方法を用いて高いデータ保持力と耐久性を供給する。

【解決手段】リフレッシュする必要があるかを判断する為にフラッシュメモリの複数のセルがテストされる。セルは読み込まれ、何れかのセルがリフレッシュが必要であるかを判断する為に複数の異なる検出比が使用される。リフレッシュが必要と判断された何れかのセルは、リフレッシュされる。セルは、単一の一定のゲート電圧のみで読み込まれる。

(もっと読む)

高速ワードラインスイッチを有するメモリ素子

【課題】ワードライン間の高速切り替えが可能なメモリ素子を提供する。

【解決手段】一実施形態において、メモリ素子は、記憶セルの配列と、各々が前記記憶セルの配列における行に対応する複数のワードラインと、各々が前記記憶セルの配列における列に対応する複数のビットラインとを具備する。前記メモリ素子は、さらに、前記複数のワードラインに接続された行デコーダを具備する。前記行デコーダは、前記複数のワードラインを個別にアサートおよびデアサートする動作が可能である。前記ワードラインの各々は、前記ワードラインが前記行デコーダに接続された位置付近に先頭部分を有する。前記メモリ素子は、前記配列の行内の複数の記憶セルにアクセスするための列デコードシーケンスをサポートする。前記列デコードシーケンスは、前記行に対応する前記ワードラインの前記先頭部分またはその付近において開始も終了もする。

(もっと読む)

メモリセルの集積回路アレイの動作方法及び集積回路

【課題】 他のワードラインをプリチャージするための時間を許容しないレイテンシ仕様を満たしつつ、複数のワードライン間のデータをコピーする。

【解決手段】 様々な方法及び装置がメモリの高速読み出しを可能とする。データの部分は、他のワードラインにコピーされて格納される。既にプリチャージされたワードラインによってアクセスされたメモリセル上に格納されたデータのコピーを読み出すことにより、第2のワードラインをプリチャージするための時間を許容しないレイテンシ仕様を満たすことができる。

(もっと読む)

1 - 10 / 13

[ Back to top ]