アイメックにより出願された特許

1 - 10 / 16

半導体装置及びその製造方法

【課題】High-k/metalゲート電極構造において各極性のFETに要求される仕事関数値を実現する。

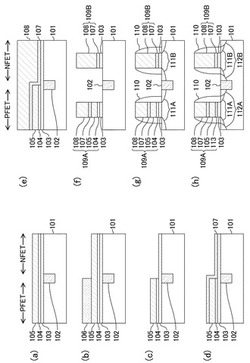

【解決手段】第1の領域と第2の領域とを有する半導体基板101の上にゲート絶縁膜103を形成する。次に、ゲート絶縁膜103の上に第1の金属窒化膜105を堆積する。次に、第1の金属窒化膜105における第2の領域に位置する部分を除去することにより、ゲート絶縁膜103における第2の領域に位置する部分を露出させる。次に、ゲート絶縁膜103における第2の領域に位置する部分の上に、第1の金属窒化膜105と同じ金属窒化物からなる第2の金属窒化膜107を形成する。

(もっと読む)

相変化メモリ及び制御方法

本発明は複数の相変化メモリセルを備える相変化メモリ装置に関し、各セルは第1電極と第2電極との間に導電的に結合された相変化材料を備え、相変化メモリ装置のプログラミングサイクルにおいて相変化材料に所定の極性のリセットパルスを加えるように構成され、更に、前記第1電極及び第2電極に結合され、最初の数のプログラミングサイクルにおいて対応するセルにリセット電流パルスが供給された後に、次の数のプログラミングサイクルにおいて対応するセルに供給されるリセット電流パルスの極性を逆転するように構成されたコントローラを備える。本発明はこのようなメモリ装置を制御する方法にも関する。  (もっと読む)

(もっと読む)

多重ビット相変化メモリセル

【解決手段】相変化メモリセルは、1個またはそれ以上のメモリ領域(14,18)を有し、これらメモリ領域は第1および第2の電極(4,6)間に延在する相変化メモリ材料(2)の狭窄部分とする。複数個のメモリ領域(14,18)はそれぞれ、電流および/または電圧の適切なプログラミング条件を加えることで、低抵抗状態または高抵抗状態にプログラムすることができる。高抵抗状態の抵抗および高抵抗状態を低抵抗状態に変換するプログラミング条件は、前記複数個のメモリ領域毎に異ならせる。  (もっと読む)

(もっと読む)

半導体デバイスの製造方法および半導体デバイス

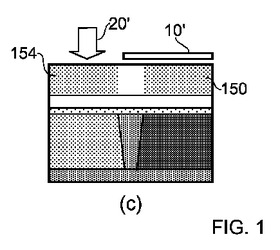

適切な仕事関数の材料のゲート電極を有する半導体デバイスの製造方法を開示する。この方法は、所定数の活性領域(110,120)および該活性領域(110,120)を被覆する誘電体層(130)を含む基板(100)を提供する工程と、前記誘電体層上に積層体(140,150,160)を形成する工程を有する。積層体の形成は、前記誘電体層(130)上に、第1の厚さ、例えば10nm未満を有する第1の金属層(140)を析出させる工程と、該第1の金属層(140)上に、第2の厚さを有する第2の金属層(150)を析出させる工程であり、前記第2の厚さが前記第1の厚さより厚い工程と、前記第2の金属層(150)にドーパント(152,154)を導入する工程と、前記デバイスを温度上昇下にさらし、前記ドーパント(152,154)の少なくとも一部を、前記第2の金属層(150)から前記第1の金属層(140)と前記第2の金属層(150)との界面を越えて、移動させる工程と、前記積層体を所定数のゲート電極(170)にパターニングする工程と、を有する。この方法によれば、ゲート電極は、誘電体層(130)の近くにドーパントプロファイルを有するように形成されるため、ゲート誘電体がドーパントの侵入により劣化することなく、ゲート電極の仕事関数を最適化することができる。  (もっと読む)

(もっと読む)

バーチカル型相変化メモリセル

バーチカル(垂直)型相変化メモリセル(2)は相変化メモリ材料の活性領域(24)を有し、この活性領域(24)は、相変化メモリ材料の一部上にのみ延在する接点を設ける、または相変化メモリ材料の一部のみを露出させる絶縁層を設けることのいずれかで画定する。1個のセルには1個以上の活性領域(24)が存在し、各セルに1ビット以上のデータを格納することができる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】適切な仕事関数を有する金属ゲート電極を備え、空乏化が抑制され、高速に動作可能な半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板1001内に形成されたp型活性領域1003およびn型活性領域1004と、p型活性領域1003の上面に形成された第1のゲート絶縁膜と、第1のゲート絶縁膜上に形成され、金属元素を含む第1の電極形成膜1007を有する第1のゲート電極とを有する第1のMISFETと、n型活性領域1004の上面に形成された第2のゲート絶縁膜と、第2のゲート絶縁膜上に形成された第2の電極形成膜1010を有する第2のゲート電極とを有する第2のMISFETとを備えている。第2の電極形成膜1010は、第1の電極形成膜1007と同じ金属元素を含み、第1の電極形成膜1007よりも酸素の含有比が高い。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化されても良好な品質を有するゲート絶縁膜を備え、信頼性が高く、高速に動作可能な半導体装置およびその製造方法を提供する。

【構成】半導体装置は、半導体基板1001内に形成されたp型活性領域1003およびn型活性領域1004と、p型活性領域1003の上面に形成されたゲート絶縁膜1006と、上部におけるLaの濃度がその他の部分のLaの濃度よりも大きい第1の電極形成膜1015を含む第1のゲート電極とを有するp型MISFETとを備えている。さらに、n型活性領域1004の上面に形成されたゲート絶縁膜1006と、上部におけるAlの濃度がその他の部分のAlの濃度よりも大きい第2の電極形成膜1014を含む第2のゲート電極とを有するn型MISFETとを備えている。

(もっと読む)

半導体装置の製造方法

【課題】金属窒化膜からなるゲート電極を有するMOSFETにおいて、ゲート電極の窒素組成を容易に制御することを可能とする半導体装置の製造方法を実現できるようにする。

【解決手段】半導体装置の製造方法は、半導体基板11の上に絶縁膜15を形成する工程(a)と、絶縁膜15の上に窒素を含まない材料かなる膜である第1の導電膜16を形成する工程(b)と、第1の導電膜16の上に窒素を含む材料からなる膜である第2の導電膜18を形成する工程(c)と、第2の導電膜18及び第1の導電膜16をパターニングしてゲート電極を形成すると共に、絶縁膜15をパターニングしてゲート絶縁膜を形成する工程(d)とを備えている。

(もっと読む)

半導体デバイスおよびこのようなデバイスの製造方法

本発明は、基板(11)および半導体本体(1)を有する半導体デバイス(10)であって、この半導体本体(1)は、順にコレクタ領域(2)、ベース領域(3)、およびエミッタ領域(4)を有するバイポーラトランジスタを備える該半導体デバイス(10)に関し、半導体本体は、コレクタ領域(2)およびベース領域(3)の少なくとも一部分を有する、突出するメサ(5)を備え、このメサを絶縁分離領域(6)によって包囲する。本発明によれば、半導体デバイス(10)は、さらに、ソース領域、ドレイン領域、介在させたチャネル領域、積層させたゲート誘電体(7)、およびゲート領域(8)を有する電界効果型トランジスタを備え、ゲート領域(8)は電界効果型トランジスタの最も高い部分を形成し、メサ(5)の高さはゲート領域(8)の高さより大きくする。このデバイスは本発明による方法によって安価かつ容易に製造することができ、このバイポーラトランジスタは優れた高周波数特性を有することができる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】低リーク電流及び低閾値電圧のnチャネルMOSトランジスタとpチャネルMOSトランジスタとが一の基板に形成された半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11の上に形成され、第1のゲート絶縁膜32及び第1のゲート電極33を有する第1導電型のトランジスタ31と、第2のゲート絶縁膜42及び第2のゲート電極43を有する第2の導電型のトランジスタ41とを備えている。第1のゲート電極33は、金属膜14aを有するメタルゲート電極であり、第2のゲート電極43は、シリサイド膜26bからなるフルシリサイド化ゲート電極である。

(もっと読む)

1 - 10 / 16

[ Back to top ]