ノースロップ グラマン システムズ コーポレーションにより出願された特許

1 - 10 / 14

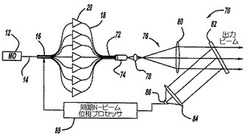

全ファイバ合成高出力コヒーレントビーム結合

【課題】改善されたフィルファクタを備えたビームを結合するためにファイバ増幅器の端部を先細のファイバ束へと結合する高出力ファイバレーザ増幅器を提供する。

【解決手段】信号ビームを生成する主発振器を含むファイバレーザ増幅器システム。スプリッタは信号ビームを複数のファイバビームへと分割し、別個のファイバビームがファイバビームの増幅のためにファイバ増幅器に送られる。先細のファイバ束は、すべてのファイバ増幅器のすべての出力端部を、結合した出力ビームを提供する組み合わされたファイバへ結合する。端部キャップは、出力ビームを拡張するために先細のファイバ束の出力端部に光学的に結合される。

(もっと読む)

横方向のオーバーモードバルク音響共振器

バルク音響共振器アセンブリおよびその共振器アセンブリを製造するための方法を提供する。共振器は、基板の第1の表面上にキャビティを含み、低音響損失材料のシートがキャビティに亘って懸吊される。低音響損失材料のシートは、低音響損失材料のシートの関連される基本周波数が、基板の第1の表面に平行する方向における低音響損失材料のシートの長さに応じるように構成される。トランスデューサは、低音響損失材料のシート上に電気機械層、および電気機械材料上に形成されたパターニングされた導電材料を含む。トランスデューサは、電気信号を導電パターンに付与すると、低音響損失材料において振動を誘発するように構成される。 (もっと読む)

グラフェン酸化物の脱酸素

【課題】費用及び危険性を伴なう、ヒドラジン、高温、不活性ガスを必要としないグラフェン酸化物の還元法を提供する。

【解決手段】グラフェン酸化物(GO)標的物を、GO標的物の脱酸素反応を開始させるのに足る出力を有する光に暴露し、光熱分解する。GO標的物の脱酸素反応中に酸素を捕捉する触媒が、ニッケル、銅、ケイ素およびマグネシウムの1種または複数である触媒を用いて、GO標的物を、200ナノメートル〜400ナノメートルの波長を有するグラフェン酸化物の薄膜をパターニングするように配置されたリソグラフィー光源からの光に暴露して、GO標的物の脱酸素反応中に酸素を捕捉する。

(もっと読む)

高沸点溶剤中でのグラフェン酸化物のグラフェンへの還元

【課題】グラフェン酸化物の水分散物を形成する工程を含むグラフェン製造方法を提供する。

【解決手段】該分散物に溶剤を加えて溶液を形成する工程、及び該溶液の温度を制御してグラフェンを形成する工程をさらに含む。グラフェン酸化物を水に分散する工程が音波処理によること。分散物がおよそ1ミリリットルの水に対しておよそ1ミリグラムのグラフェン酸化物の割合で含むこと。溶剤が水混和性溶剤であること。水混和性溶剤がn−メチルピロリドン、エチレングリコール、グリセリン、ジメチルピロリドン、アセトン、テトラヒドロフラン、アセトニトリル、ジメチルホルムアミド、アミン、及びアルコールの少なくとも1つであること。分散物に溶剤を加える工程が前記分散物の量とおよそ等量の溶剤を加えること。

(もっと読む)

ガードリング構造およびその製造方法

半導体素子用のガードリング構造。ガードリング構造は、第1層および第1層の上面に第2層を有する半導体積層体と、第1層内に形成されたゲート構造と、第1層内に形成されたガードリングとを有する。第2層は、第1層のドーパント濃度よりも高いドーパント濃度を有する。ゲートおよびガードリングは、単一のマスクを用いて同時に形成される。  (もっと読む)

(もっと読む)

エッジ終端性能改善のための電場停止層を備えた半導体構造

例示のエッジ終端構造は、半導体素子の周囲に電場停止層を形成することによって、ウエハから切断され実装された後に半導体素子の降伏電圧を維持する。電場停止層は、ドリフト層またはチャネル層のようなエッジ終端構造が提供された層のものより高いドーパント濃度を有する。電場停止層は、素子の周囲に高濃度でドープされた材料を保護し維持するため、素子の製造工程、すなわちメサエッチング中に素子の周囲を選択的にマスキングすることによって形成される。  (もっと読む)

(もっと読む)

化合物半導体MMICにおける信頼性の改良

半導体パッケージ(M)が、第一の側面または上面(120)および第一の側面(120)とは反対の第二の側面または下面(背面)(104)を有する。熱生成領域(120)が半導体基板層(100)の第一の側面(120)に関連して形成される。ダイ接着部材(106)が半導体基板層(100)の第二の側面(104)に接して形成され、半導体基板層(100)の第二の側面(104)の全体よりも小さい範囲にわたって伸張する。ダイ接着部材(106)は半導体基板層(100)に関して熱生成領域(102)と反対側に一様に位置する。  (もっと読む)

(もっと読む)

大領域SiC基板の製造方法

Si基板上にSiC含有フィルムを成長させるための方法が開示される。SiC含有フィルムは、例えば、プラズマスパッタリング、化学気相成長法または原子層堆積により、Si基板上に形成することができる。このようにして成長されたSiC含有フィルムは、半導体結晶の成長用の高価なSiCウェハーの代わりに提供される。  (もっと読む)

(もっと読む)

改良された電力用スイッチングトランジスター

実施例によれば、半導体集積デバイスが、ソースとこのソースの各々の側部に配置されたゲートを有する第1の垂直接合電界効果トランジスター(Vertical Junction Field Effect Transistor: VJFET)と、ソースとこのソースの各々の側部に配置されたゲートを有する第2の垂直接合電界効果トランジスターを含む。第1の垂直接合電界効果トランジスター(VJFET)の少なくとも1つのゲートは、第2のVJFETの少なくとも1つのゲートから、チャンネルにより分離される。半導体集積デバイスは、更に、第1と第2のVJFETの間に配置された接合バリアーショトキー(Junction Barrier Schottky:JBS)ダイオードを含む。このJBSダイオードは、このチャンネルに対する整流コンタクトを構成し、かつ、第1と第2のVJFETの少なくとも1つのゲートに対する非整流コンタクトを構成する金属コンタクトを備え、この金属コンタクトが、このJBSダイオードのアノードである。第1の電気接続手段が、第1のVJFETのゲート、第2のVJFETのゲート、及び、JBSダイオードのアノードを、共通ゲート電極に連結し、及び、第2の電気接続手段が、第1のVJFETのソースと第2のVJFETのソースを、共通ソース電極に連結する。  (もっと読む)

(もっと読む)

ワイドバンドギャップ半導体デバイス用ゲート駆動部

【課題】小型で、費用効率の良い半導体接合型ゲートトランジスタ用制御回路を提供する。

【解決手段】ゲート電流制限抵抗器445は、使用時にワイドバンドギャップ半導体接合ゲートトランジスタのゲート入力に結合され、接合ゲートトランジスタのゲートに入力されるゲート電流を制限する。AC結合充電コンデンサ435は、使用時にワイドバンドギャップ半導体接合ゲートトランジスタのゲート入力に結合され、ゲート電流制限抵抗器445に並列に配置されている。ダイオード430は、ゲート電流制限抵抗器445及びAC結合充電コンデンサ435に、ゲート駆動チップの出力に結合されている。使用時に、ダイオード430は、ゲート電流制限抵抗器445を介してワイドバンドギャップ半導体接合ゲートトランジスタのゲート入力に印加され、ゲート駆動チップからのゲート電圧出力を低下させる。

(もっと読む)

1 - 10 / 14

[ Back to top ]