エルエスアイ コーポレーションにより出願された特許

101 - 110 / 124

仮想化サーバ・プラットフォーム上でブート可能な仮想ストレージ・アプライアンスをブートするためのシステムおよび方法

一実施形態は、仮想化サーバ・プラットフォーム上でブート可能な仮想ストレージ・アプライアンスをブートするための方法である。そのような一方法は、サーバ・プラットフォームに、複数のディスクを含むディスクアレイを管理するように構成された仮想ストレージ・アプライアンスを提供することであって、ディスクのうちの少なくとも1つがブート・コンソールを有する隠しブート・パーティションを含む、仮想ストレージ・アプライアンスを提供することと、サーバ・プラットフォームを起動することと、ブート・コードをサーバ・プラットフォームにロードすることと、ブート・コンソールを隠しブート・パーティションからロードすることと、ブート・コンソールが、仮想化環境のためのブート・コンポーネントをロードすることとを含む。  (もっと読む)

(もっと読む)

仮想化されたサーバ・プラットフォーム上に起動可能な仮想ストレージ・アプライアンスをインストールするためのシステムおよび方法

一実施形態は、ホスト・サーバ・プラットフォーム上に仮想ストレージ・アプライアンスをインストールするための方法である。1つのそのような方法は、ホスト・サーバ・プラットフォームにインストール・パッケージを供給し、このインストール・パッケージが、IOVM(I/O仮想マシン)をインストールするためのインストール・スクリプトと、IOVMブート・コンソールと、IOVM管理モジュールとを備えること、インストール・スクリプトを実行して、ブート・ディスク上に、隠されたブート・パーティションを作成し、その隠されたブート・パーティションにIOVMブート・コンソールおよびIOVM管理モジュールをコピーすること、ホスト・サーバ・プラットフォームを再起動すること、隠されたブート・パーティションからIOVMブート・コンソールおよびIOVM管理モジュールを読み込むこと、IOVM管理モジュールを介してディスク・アレイを構成すること、このアレイの中の各ディスクに関して、隠されたブート・パーティションを作成して、IOVMブート・コンソールおよびIOVM管理モジュールをレプリケートすること、ならびにIOVMブート・コンソールをストレージ・ドライバとして使用して仮想ストレージ環境をインストールすることを備える。  (もっと読む)

(もっと読む)

フラッシュ・メモリにおける書き込み側セル間干渉軽減のための方法および装置

フラッシュ・メモリにおける書き込み側セル間干渉軽減のための方法および装置が提供される。フラッシュ・メモリにおける少なくとも1つのターゲット・セルに書き込まれるべきプログラム・データを獲得すること、このターゲット・セルより後にプログラミングされるべき少なくとも1つのアグレッサ・セルに関するプログラム・データの1つまたは複数のビットを獲得すること、および事前補償されたプログラム値を生成することによって、このターゲット・セルに関するセル間干渉を事前補償することによって、フラッシュ・メモリ・デバイスに書き込みが行われる。アグレッサ・セルは、ターゲット・セルと同一のワード線における隣接セル、および/またはターゲット・セルの上位または下位の隣接するワード線におけるセルなどの、ターゲット・セルに隣接する1つまたは複数のセルを備える。ターゲット・セルに関する事前補償されたプログラム値は、オプションとして、フラッシュ・メモリに供給される。  (もっと読む)

(もっと読む)

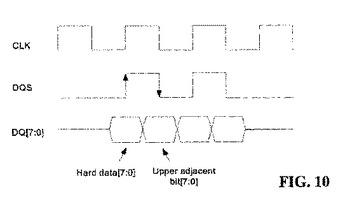

フラッシュ・メモリ・コントローラとフラッシュ・メモリ・アレイの間でインタフェースをとるための方法および装置

フラッシュ・メモリ・コントローラとフラッシュ・メモリ・アレイの間でインタフェースをとるための方法および装置が提供される。このインタフェースは、フラッシュ・メモリ・コントローラとフラッシュ・メモリ・アレイの間の通信チャネルを備え、この通信チャネルは、クロック信号の第1のエッジでフラッシュ・メモリ・アレイにおけるターゲット・セルに関するデータを伝送し、さらにこの通信チャネルは、クロック信号の第2のエッジで、そのターゲット・セルに関するさらなる情報を伝送する。例示的な書き込みアクセスの場合、さらなる情報は、例えば、ターゲット・セルに関連する1つまたは複数のアグレッサ・セルについての情報を備える。例示的な読み取りアクセスの場合、さらなる情報は、例えば、第1のエッジで伝送されるターゲット・セルに関するデータに関するソフト情報を備える。  (もっと読む)

(もっと読む)

変調コーディングを使用するセル間干渉軽減のための方法および装置

変調コーディングを使用するセル間干渉軽減のための方法および装置が提供される。フラッシュ・メモリのプログラミング中に、1つまたは複数の事前定義された基準に違反する値でプログラミングされるフラッシュ・メモリにおけるセルの数が、より少なくなるようにフラッシュ・メモリをプログラミングするための1つまたは複数のレベルを選択する変調符号化が、実行される。フラッシュ・メモリの読み取り中に、1つまたは複数の事前定義された基準に違反する値で読み取られるフラッシュ・メモリにおけるセルの数が、より少なくなるようにフラッシュ・メモリにおけるセルに1つまたは複数のレベルを割り当てる変調復号が、実行される。事前定義された基準は、例えば、プログラミングされたセルによってもたらされる妨害の量、プログラミングされたセルの電圧シフト、プログラミングされたセルによって格納される電圧、プログラミングされたセルを流れる電流の変化の量、およびプログラミングされたセルを流れる電流の量の1つまたは複数に基づくことが可能である。  (もっと読む)

(もっと読む)

フラッシュ・メモリにおける読み取り側セル間干渉軽減のための方法および装置

フラッシュ・メモリにおける読み取り側セル間干渉軽減のための方法および装置が提供される。少なくとも1つのターゲット・セルに関する読み取り値を獲得すること、このターゲット・セルより後にプログラミングされた少なくとも1つのアグレッサ・セルの中に格納された電圧を表す値を獲得すること、少なくとも1つのアグレッサ・セルからのターゲット・セルに関するセル間干渉を算出すること、および算出されたセル間干渉を少なくとも1つのターゲット・セルに関する読み取り値から除去することによってセル間干渉を補償する新たな読み取り値を獲得することによって、フラッシュ・メモリ・デバイスが読み取られる。この新たな読み取り値は、オプションとして、復号器に供給されることが可能である。反復型の実施例において、復号誤りが生じた場合、1つまたは複数のセル間干渉軽減パラメータが調整されることが可能である。  (もっと読む)

(もっと読む)

フラッシュ・メモリにおけるソフト・デマッピングおよびセル間干渉軽減のための方法および装置

フラッシュ・メモリにおけるソフト・デマッピングおよびセル間干渉軽減のための方法および装置が提供される。一変種において、1セル当り少なくとも2つのデータ・レベル、sを格納することができるフラッシュ・メモリ・デバイスにおけるターゲット・セルが、フラッシュ・メモリにおける少なくとも1つのターゲット・セルに関する測定された読み取り値、rを獲得すること、フラッシュ・メモリにおける少なくとも1つのアグレッサ・セルに関して格納されたデータを表す値、hを獲得すること、フラッシュ・メモリの少なくとも一部分の中に格納された値のパターンに基づいて、フラッシュ・メモリにおける少なくとも1つのターゲット・セル上の、1つまたは複数のアグレッサ・セルのパターン依存の妨害を備える1つまたは複数の確率密度関数を選択すること、測定された読み取り値、rに基づいて、選択された少なくとも1つの確率密度関数を評価すること、および評価するステップの結果に基づいて、1つまたは複数の対数尤度比を計算することによって読み取られる。  (もっと読む)

(もっと読む)

複数のコード・タイプをプログラマブル復号する方法および装置

複数のコード・タイプをプログラマブル復号するための方法および装置が提供される。それぞれが通信規格に対応する複数のコード・タイプのうちの1つを使用して符号化されたデータを復号するための方法が提供される。データに関連するコード・タイプが識別され、データが、複数のプログラマブルな並列デコーダに割り当てられる。プログラマブルな並列デコーダは、複数のコード・タイプのそれぞれを使用して符号化されたデータを復号するように再構成可能である。通信ネットワークを使用してM個の並列デコーダ間でデータをインタリーブするための方法も提供される。インタリーバ・テーブルが使用され、インタリーバ・テーブルの各エントリが、インタリーブされたデータのターゲット・デコーダおよび通信ネットワークのターゲット・アドレスとして、M個の並列デコーダのうちの1つを識別する。データは、通信ネットワークのターゲット・アドレスにデータを書き込むことによってインタリーブされる。通信ネットワークは、たとえばクロスバー・スイッチおよび/または1つまたは複数の先入れ先出しバッファを備えることができる。  (もっと読む)

(もっと読む)

ラッチベースのアナログ−デジタル変換のためのシステム及び方法

本発明の種々の実施例はラッチベースのアナログ−デジタル変換のシステム及び方法を提供する。例えば、コンパレータのセット、セレクタ回路及びラッチ部を有する第1のインターリーブ部を含むラッチベースのアナログ−デジタルコンバータが開示される。コンパレータのセットはアナログ入力をそれぞれの基準電圧と比較するよう動作し、クロック位相に同期される。セレクタ回路はセレクタ入力に少なくともある程度基づいてコンパレータのセットのうちの1つの出力を選択するよう動作する。選択された出力から第1のインターリーブ出力が引き出される。ラッチ部は第2のインターリーブ部から第2のインターリーブ出力を受け、クロック位相がアサートされるとトランスペアレントとなる。セレクタ入力はラッチ部の出力を含む。  (もっと読む)

(もっと読む)

同期タイミング再設定アナログ−デジタル変換のためのシステム及び方法

本発明はアナログ−デジタル変換のためのシステム及び方法を提供する。第1及び第2のセットのサブレベルインターリーブ部を含むタイミング再設定アナログ−デジタルコンバータの回路が開示される。第1のセットのサブレベルインターリーブ部は第1のクロック位相に同期される第1のセットのコンパレータを有する第1のサブレベルインターリーブ部、及び第2のクロック位相に同期される第2のセットのコンパレータを有する第2のサブレベルインターリーブ部を含む。第2のセットのサブレベルインターリーブ部は第3のクロック位相に同期される第3のセットのコンパレータを有する第3のサブレベルインターリーブ部、及び第4のクロック位相に同期される第4のセットのコンパレータを有する第4のサブレベルインターリーブ部を含む。グローバルインターリーブ部は第2のセットのサブレベルインターリーブ部からの出力に基づいて第1のセットのコンパレータのうちの1つを選択する。  (もっと読む)

(もっと読む)

101 - 110 / 124

[ Back to top ]