エルエスアイ コーポレーションにより出願された特許

41 - 50 / 124

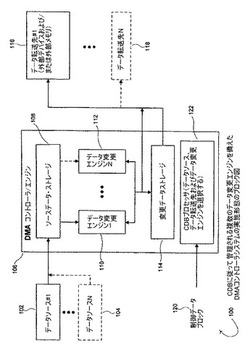

同時データ操作が可能なDMAエンジン

【課題】DMAコントローラ/エンジンによって管理される直接メモリアクセス(DMA)・チャネルを介して転送されるデータ上で、複数のデータ操作オペレーションを同時に実行するための方法およびデバイスを提供する。

【解決手段】DMAコントローラ内部で動作する制御データブロック(CDB)プロセッサは、CDBを読み出し、CDBの内容に従ってデータの読み出し、データ操作オペレーションおよびデータの書き込みを設定してもよい。データがDMAコントローラを通して導かれる間に、例えばハッシング、HMAC、フィルパターン、LFSR、EEDP検査、EEDP生成などの複数のデータ操作オペレーションをデータ上で同時に実行してもよい。データ操作オペレーションを実行するデータ変更エンジンは、データ操作オペレーションの間に外部メモリへのアクセスを回避するために局所RAMを使用する、DMAコントローラ上で実施されてもよい。

(もっと読む)

データ回復のためのシステムおよび方法

【課題】データ回復のためのシステムおよび方法を提供する。

【解決手段】記憶媒体上の再現可能なロケーションを識別するためのシステムおよび方法を提供する。識別回路は、媒体欠陥検出回路112およびアンカ固定回路114を含む。媒体欠陥検出回路112は、媒体欠陥を識別するように動作可能であり、アンカ固定回路114は、その媒体欠陥を基準とするロケーションを識別するように動作可能である。このロケーションは、再現可能である。

(もっと読む)

ハードディスク欠陥領域の検出および分類のための周波数に基づく方法

【課題】TMR読取ヘッドを使用するハードディスクドライブにおいてMDおよびTA領域を検出および分類するのに使用する方法を提供すること。

【解決手段】ハードディスクドライブリードチャネルにおいて、ADCまたは等化器の出力値などの信号値に、離散型フーリエ変換(DFT)などの変換を適用することによって、ハードディスク上に記憶される2Tのデータパターンなどに対応する、周波数に基づく評価量が、2つの異なるデータ周波数(たとえば2TおよびDC)で生成される。この周波数に基づく評価量は、ハードディスク上の欠陥領域を検出し、かつ/または、欠陥領域を熱凹凸(TA)もしくはドロップアウト・媒体欠陥(MD)のいずれかの原因に分類するのに使用される。

(もっと読む)

ステップ遅延事前補償を伴う適応クロック回復

【課題】ステップ遅延事前補償を伴う適応クロック回復を提供する。

【解決手段】ACR(適応クロック回復)サブシステムが、ジッタのあるパケット着信時間を示す入力位相信号を処理して、比較的安定した、回復されたクロック信号を生成するのに使用され得る、比較的平滑で、範囲が限られた出力位相信号を生成する。また、入力位相信号は、例えば、パケットのネットワーク・ルーティングのパス変更に対応する、ステップ遅延を検出し、測定するようにも処理される。入力位相信号が、検出された各ステップ遅延の符号および大きさに基づいて、ACRサブシステムの上流で位相調整されるステップ遅延事前補償が、実行される。その結果、ACRサブシステムは、そのようなステップ遅延の存在に実質的に気付かない。

(もっと読む)

閉ループ・ソフト・エラー率感度制御

【課題】電子回路への放射線の攻撃に起因するソフト・エラー率(SER)を制御するための閉ループ・フィードバック・システムを提供すること。

【解決手段】可変感度ソフト・エラー率検出器が、そのソフト・エラー率に対応した出力を提供する。その出力は、電圧制御に供給される。その電圧制御の出力は、センサの感度制御にフィードバックされ、それによりフィードバック・ループを形成する。この電圧制御の出力は、ソフト・エラー率センサの電源でもよい。このソフト・エラー率センサの出力はまた、フォールトトレランス方式を有効および無効にするために、あるいはユーザに警告するために使用されることができる。

(もっと読む)

汎用プロセッサ上の信号処理を用いるメモリ読取チャネル

メモリ・デバイスの読取チャネル内のデータ値を処理する方法および装置を提供する。データ値は、処理のために汎用プロセッサに提供される。データ値は、復号されたデータではなく、生データ値および中間データ値のうちの1つまたは複数を含むことができる。データ値を、たとえば1つまたは複数の事前定義のトリガ条件の検出時に、汎用プロセッサに供給することができる。データ値を、メモリ・デバイスから入手し、その後、汎用プロセッサにリダイレクトすることができる。データ値は、復号されたデータではない。リダイレクションを、1つまたは複数の事前定義のバイパス条件が存在する場合に条件付きで実行することができる。汎用プロセッサは、オプションで、1つまたは複数の追加アプリケーションと共に時分割される。  (もっと読む)

(もっと読む)

タイミング回復ループのための位相検出器

【課題】タイミング回復ループのための位相検出器を提供する。

【解決手段】(ハードドライブ)読取りチャネルはタイミング回復ループで使用される位相検出器を有する。位相検出器は受信対数尤度比(LLR)信号からの符号ビット及び信頼度値を利用して平均値を生成する。平均値は部分応答目標値で畳み込まれて推定タイミングエラー信号を生成する。位相検出器は、ハードドライブ読取りチャネルで実施されるときに、より低いロス・オブ・ロック比でのタイミング回復を可能とする。

(もっと読む)

自動フィルタリセット機構

【課題】ハードドライブのセクタ内の読み出し動作時に、ハードドライブのリードチャネル内のデジタル有限インパルス応答(DFIR)フィルタなどの等化フィルタを自動的にリセットするための機構を提供する。

【解決手段】一実施形態では、(ハードドライブ)リードチャネルは、(DFIR等化)フィルタを有し、そのタップ係数は適応的に更新される。リセット・コントローラは、例えばユーザ指定のタップ係数の初期セットを再ロードすることにより、フィルタをいつリセットするかを自動的に判定するために、フィルタのダウンストリームで発生される(LLR)信号を監視する。LLR値に対して、リセット・コントローラは、低過ぎる信頼値を有する最近のLLR値が多過ぎることをリセット・コントローラが検出したときに、フィルタをリセットするように判定する。ハードドライブ・リードチャネル内に実施されたときは、リセット・コントローラは、ハードドライブのセクタ内の読み出し動作の間に1回または複数回、フィルタをリセットすることができる。

(もっと読む)

反復復号における位相依存データ検出のためのシステムおよび方法

【課題】データ処理のためのシステムおよび方法を提供する。

【解決手段】データ処理回路は、第1のデータ検出回路であって、データセットに対して位相依存データ検出アルゴリズムを適用し、それにより第1のデータ検出回路の第1の出力は、第1のデータ検出回路に渡されたデータセットの位相に応じて変化する、第1のデータ検出回路を含む。データセットの第1の位相は、第1のデータ検出回路に渡される。復号出力を生じるように第1の出力に復号アルゴリズムを適用するデコーダ回路と、データセットの第2の位相が、位相シフトされた出力として供給される復号出力を位相シフトする位相シフト回路とを含む。第2の検出回路は、位相シフトされた出力に位相依存データ検出アルゴリズムを適用し、第2のデータ検出回路の第2の出力は少なくとも部分的に、第2のデータ検出回路に渡されたデータセットの異なる位相により第1の出力から変化するようになる。

(もっと読む)

高速サンプリング位相再生

【課題】サンプリング位相を再生するための技術を提供する。

【解決手段】通信受信機において、タイミング再生回路は第1の通信装置のタイミング再生ループと関連するループフィルタを含む。第1の通信装置は第1の通信装置における一時的なパワーダウン/パワーアップシーケンスの前に第2の通信装置と通信している。ループフィルタは(i)第1の通信装置における一時的なパワーダウン/パワーアップシーケンス後にタイミング再生ループの少なくとも一部を一時的に無効にするように、及び(ii)第1の通信装置が第2の通信装置との通信を再開することができる所与のサンプリング位相を決定するために一連の可能性のあるサンプリング位相によりプログレッションを開始するように構成されている。

(もっと読む)

41 - 50 / 124

[ Back to top ]