エルエスアイ コーポレーションにより出願された特許

11 - 20 / 124

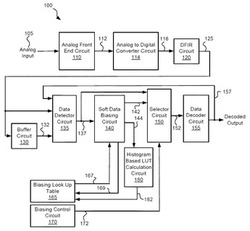

非二値復号バイアス制御のためのシステム及び方法

【課題】データ処理のためのシステム及び方法を提供する。

【解決手段】データ検出器回路と、バイアス回路と、データ復号器回路とを備えるデータ処理回路。データ検出器回路は、一連のシンボルにデータ検出アルゴリズムを適用して検出出力をもたらすように動作可能であり、検出出力は非二値シンボルに対応する一連の軟判定データを含む。バイアス回路は、一連の軟判定データのそれぞれにバイアスを適用して一連の被バイアス軟判定データをもたらすように動作可能である。データ復号器回路は、非二値シンボルに対応する一連の被バイアス軟判定データにデータ復号アルゴリズムを適用するように動作可能である。

(もっと読む)

側面アクセス可能なドライブ・スレッド内に記憶デバイスを有する装置およびシステム

【課題】 記憶筐体(102)内に搭載されたスレッド(104)の側面から記憶デバイス(106)への、改良されたアクセスのための装置およびシステムを提供すること。

【解決手段】 実施形態は、スレッドが筐体から前方に引き出されるときに、スレッドの各側面上の記憶デバイス(106)へのアクセスを提供する、記憶筐体内のスレッドのための装置およびシステムを提供する。筐体内の記憶デバイスの一部へのアクセスを可能にするために、複数のスレッドが1つの筐体内に封入されてよく、それにより、筐体がラックの頂部付近に搭載される場合に、ラックが不安定になる問題が低減される。

(もっと読む)

オーバサンプリングされたアナログ・デジタル変換を備えるリード・チャネル

【課題】オーバサンプリングされたアナログ・デジタル変換を使用して、リード・チャネルの中の信号を処理するための方法および装置を提供すること。

【解決手段】アナログ入力信号に対してオーバサンプリングされたアナログ・デジタル変換を実行して、所与のビット間隔についてアナログ入力信号に対応する複数のデジタル・サンプルを生成する。次いで、デジタル・サンプルのうちの1つまたは複数に対してデータ検出アルゴリズムを適用して、検出された出力を取得することができる。オーバサンプリングされたアナログ・デジタル変換は、等化処理および/またはフィルタリング処理の少なくとも一部をデジタル領域に移すことにより、アナログ設計を簡略化する。

(もっと読む)

表面欠陥を早期に検出するプレスキャン機能を有する光ディスク再生デバイス

【課題】プレスキャン機能を実施することによって、表面欠陥が存在するときの光ディスク再生デバイスの読み出し性能を向上させる。

【解決手段】光ディスク再生デバイスは、第1および第2のレーザと、光学アセンブリと、第1および第2の光学検波器と、光学検波器に結合されたコントローラ回路とを備える。光学アセンブリは、第1および第2のレーザからの入射光を光ディスクの表面上にそれぞれ前走査スポットおよび後走査スポットを形成するように導くように構成され、さらに、光ディスクの表面上の前走査スポットおよび後走査スポットからの対応する反射光をそれぞれの光学検波器に導くように構成される。コントローラ回路は、後走査スポットが光ディスクの表面欠陥に到達する前に前走査スポットに関連する反射光を処理することによって光ディスクの表面欠陥を識別するように構成される。

(もっと読む)

ユーザーデータに基づくフライハイト計算のためのシステム及び方法

【課題】読取り/書込みヘッドのフライハイトをユーザデータに基づいて正確に予測し、計算するシステムおよび方法を提供する。

【解決手段】ユーザデータ内の第1のパターンに対応するデータを用いて第1のフライハイトを計算し、さらに平均化された出力を得る第1の平均化回路と、ユーザデータ内の第2のパターンに対応するデータを用いて第2のフライハイトを計算し、さらに平均化された出力を得る第2の平均化回路と、少なくとも第1の平均化された出力および第2の平均化された出力を結合して複合フライハイト値を得る結合回路とを備える。第1のパターンは第1の周期的なパターンであり、第2のパターンは第2の周期的なパターンであることが望ましい。

(もっと読む)

第1のサイズの記憶装置を第2のサイズの記憶装置用のスロットに適合させるための記憶装置キャリア

【課題】記憶装置を異なる形式の記憶装置用のスロットに適合するキャリアを提供する。

【解決手段】キャリア(300)はその元の形状から弾性的に形状変形をする開き手段(304)を含み、記憶装置を受容できるようにしている。キャリア(300)が元の形状に戻ったときに、キャリア(300)内の記憶装置の動きを抑止する抑制手段(306)を更に含む。記憶装置(200)がキャリア(300)内に抑止されている間、記憶装置(200)とスロットを整列させている間隔手段(302)を含む。

(もっと読む)

集積回路テスト用の低電力で面積効率の良いスキャンセル

【課題】電力消費および面積要件の低減がもたらされる、スキャンテスト回路を有する集積回路を提供すること。

【解決手段】集積回路は、スキャンテスト回路と、スキャンテスト回路を使用してテストを受ける追加回路とを備える。スキャンテスト回路は、複数のスキャンセルを有する少なくとも1つのスキャンチェーンを備え、スキャンチェーンは、スキャンシフト動作モードではシリアル・シフトレジスタとして動作し、機能動作モードでは追加回路の少なくとも一部分からの機能データを捕捉するように構成される。スキャンチェーンのスキャンセルの少なくとも所与の1つは、スキャンシフト動作モードではスキャンセルの機能データ出力をディスエーブルし、機能動作モードではスキャンセルのスキャン出力をディスエーブルするように構成された出力制御回路を備える。

(もっと読む)

ダイバーシティ組合せデータ検出のシステムおよび方法

【課題】データ処理に関するシステムおよび方法を提供すること。

【解決手段】たとえば、本発明のいくつかの実施形態は、それぞれが同一の一連のデータ・サンプルを受け取り、第1検出データ出力および第2検出データ出力を供給するように動作可能な少なくとも2つのデータ検出器回路を有するパターン検出回路を含むデータ処理回路を提供する。さらに、パターン検出回路は、少なくとも部分的に第1検出データ出力および第2検出データ出力に基づいてパターン発見出力をアサートするように動作可能な結果組合せ回路を含む。

(もっと読む)

SASエキスパンダ接続ルーティング技法

【課題】シリアルアタッチドSCSIエキスパンダネットワークのトポロジサイズを増大すること、ならびにそのシステムトポロジに関するアドレス位置を格納するために使用される、コンテンツアドレス指定可能メモリ内のエントリーを限定することを可能にする技法を提供する。

【解決手段】一方法によれば、ルックアップテーブルエントリーを削減するために、アドレスがそのOAF要求内に提供される。もう1つの実施形態によれば、アドレス範囲が前記ルックアップテーブル内に提供される。加えて、最近最も使用されたアドレスだけがそのルックアップテーブル内に格納されるように、ソフトウェア探索プロセスが使用され得るか、またはハードウェアプロセスが使用され得るように、仮想メモリ技法が使用される。

(もっと読む)

メモリ・バックアップのための電力分離

【課題】電力分離およびバックアップ・システムを開示すること。

【解決手段】電源異常状態が検出される時に、一時ストレージをSDRAMにフラッシュする。フラッシュの後に、インターフェースを停止し、電力を、SDRAMサブシステムを除くチップの大半から除去する。SDRAMサブシステムは、データをSDRAMからフラッシュ・メモリにコピーする。その途中で、データを暗号化し、かつ/またはデータ完全性署名を計算することができる。データを復元するために、SDRAMサブシステムは、データをフラッシュ・メモリからSDRAMにコピーする。その途中で、復元されるデータを暗号化解除し、かつ/またはデータ完全性署名をチェックすることができる。

(もっと読む)

11 - 20 / 124

[ Back to top ]