ヒューレット−パッカード デベロップメント カンパニー エル.ピー.により出願された特許

41 - 50 / 155

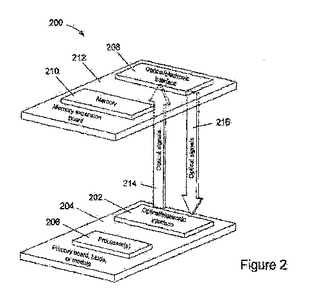

光学メモリ拡張

本発明の様々な実施形態は、コンピュータシステムのメモリを分離するための光学ベースの方法と拡張メモリシステムに向けられたものである。一態様において、拡張メモリシステム(200)は、プロセッサと電気的に連通している第1の光学/電気インターフェース(202)と、メモリと共に構成されたメモリ拡張ボード(204)と、前記メモリ拡張ボードに取り付けられた第2の光学/電気インターフェース(208)とを備える。前記第1のインターフェースは、光学信号を、前記プロセッサに送られる電気信号へと変換し、及び、前記プロセッサにより生成された電気信号を、光学信号へと変換する。前記第2のインターフェースは、光学信号を、前記メモリに送られる電気信号へと変換し、及び、前記メモリにより生成された電気信号を、光学信号へと変換する。前記光学信号は、前記第1のインターフェースと第2のインターフェースとの間において交換される。実施形態はまた、データを送って拡張メモリシステム内において受け取るための方法も含む。  (もっと読む)

(もっと読む)

ハードイメージング装置及びハードイメージング方法

ハードイメージング装置及び方法が開示される。一実施形態によれば、ハードイメージング装置は、媒体経路に沿って媒体を移動させるよう構成された媒体搬送システムと、該媒体経路に隣接するプリント装置であって、液体マーキング剤の複数の小滴を、前記媒体経路に沿って移動する前記媒体に向かう方向に噴出し、該媒体を使用してハードイメージを形成するよう構成された、プリント装置とを含む。該プリント装置による液体マーキング剤の小滴の噴出によって、該プリント装置及び前記媒体に隣接する領域の空気中に浮遊する前記液体マーキング剤のサテライトが生じる。該装置はまた、一実施形態では、該プリント装置及び前記媒体に隣接する領域の空気中から前記サテライトを除去するサテライト除去システムを含む。 (もっと読む)

面内電気光学ディスプレイ

一実施形態において、ディスプレイ要素は、第1の電極と、第1の基板を覆う、窪み領域を有する誘電体層と、誘電体層の上に配置された第2の電極と、当該ディスプレイ要素中の着色剤粒子を有する流体とを含み、第1の電圧信号が、着色剤粒子を窪み領域に密集させることによって第1の光学的状態を生成し、第2の電圧信号が、流体中の着色剤粒子を拡散させることによって第2の光学的状態を生成するように、第1の電極及び第2の電極に印加される電圧信号が、着色剤粒子の動きを制御する。 (もっと読む)

グリッドヒートシンク

グリッドヒートシンク(400)であって、

ベース(420)と、複数の交差するフィン(410,415)と、該交差するフィンにより形成された複数のチャネル(405)とを含むグリッドヒートシンク(400)。該複数のチャネル(405)の各々が、該グリッドヒートシンク(400)の入力側で冷却用空気(1605)を受容して、該冷却用空気(1605)を該グリッドヒートシンク(400)の出力側の出口へ導く。

(もっと読む)

電力分配装置・デバイス間の相関

【課題】電力分配装置・デバイス間の相関を提供する。

【解決手段】電力分配器(1つまたは複数)とデバイス(1つまたは複数)との間の相関を提供することと関連する、装置、方法、および他の実施形態が記載される。

1つの例示の方法は、電力分配器(PDU)単位でのPDUの組から引き出される電流を特定する、第1の時系列データを格納するステップを含む。例示の方法は、デバイス単位での関連デバイスの組によって使用される電力を特定する、第2の時系列データを格納するステップを含んでもよい。利用可能な2つの時系列データを用いて、方法は次に、PDUから引き出される電流とデバイスによって使用される電力との間の相関を特定する、PDU・デバイス相関信号を供給してもよい。  (もっと読む)

(もっと読む)

間接遷移型半導体の発光ダイオード

間接遷移型半導体の発光ダイオード(401)。間接遷移型半導体の発光ダイオード(401)は複数の部分を含み、前記複数の部分が、間接遷移型半導体のpドープド部分(412)、間接遷移型半導体の真性部分(414)及び間接遷移型半導体のnドープド部分(416)を含む。真性部分(414)がpドープド部分(412)とnドープド部分(416)との間に配置されて、pドープド部分(412)とp−i接合部(430)を形成し、nドープド部分(416)とi−n接合部(434)を形成する。p−i接合部(430)及びi−n接合部(434)は、間接遷移型半導体の発光ダイオード(401)が逆バイアスされる際に真性部分(414)で少なくとも1つのホットエレクトロン−正孔プラズマの形成を容易にし且つホットエレクトロンの正孔との再結合により生成されるルミネッセンスを容易にするように構成される。 (もっと読む)

三相容量ベース検知

検知を行うための様々なシステム及び方法が提供される。一実施形態において、検知システムが提供される。該検知システムは、プルーフマス上に配置された第1の電極アレイと、支持構造の平面表面上に配置された第2の電極アレイとを備える。前記第1の電極アレイが、前記第2の電極アレイに対して面するように且つほぼ平行に位置付けられることとなるように、コンプライアントな結合を介して該プルーフマスが前記支持構造に取り付けられており、及び、該プルーフマスは、前記支持構造に対して変位することが可能である。該第1の電極アレイは、複数の第1パターンの電極を含み、該第2の電極アレイは、複数の第2パターンの電極を含む。前記検知システムは、前記第1の電極アレイについての電気的なヌル位置を生成するために、前記第2パターンの電極の各々に対して入力電圧を提供するよう構成された回路構成を更に備える。  (もっと読む)

(もっと読む)

アナライザ及びアナライザを用いて検知を行うための方法

本明細書内においてアナライザ(10,10',10'')が開示されている。該アナライザ(10,10',10'')は、表面(S)内に形成された複数の異なるV字グルーブ(14)を有した該表面(S)を有する基板(12)を含む。入力フローチャンネル(16I)が、それぞれの入力ポイント(PI)において前記複数の異なるV字グルーブ(14)の各々と交差して液体連通するよう構成されており、及び、出力フローチャンネル(16O)が、それぞれの出力ポイント(PO)において前記複数の異なるV字グルーブ(14)の各々と交差して液体連通するよう構成されている。  (もっと読む)

(もっと読む)

ボイドパンタグラフを使用する方法

ボイドパンタグラフ(12)を使用する方法は、複合ボイドパンタグラフ(12,TP)を含むテストシート(10)を生成することを伴う。ここで、前記複合ボイドパンタグラフ(12,TP)のそれぞれは、パンタグラフ前景(14)及びパンタグラフ背景(16)を含む。前記テストシート(10)が印刷され、前記印刷されたテストシート(10)から、隠され又は半ば隠されているパンタグラフ前景(14)及びパンタグラフ背景(16)を有する前記複合ボイドパンタグラフ(12,TP)の少なくとも1つが識別される。前記印刷されたテストシート(10)がスキャンされ、前記スキャンされたテストシート(10)から、顕在化したパンタグラフ前景(14)を有する前記複合ボイドパンタグラフ(12,TP)の少なくとも1つが識別される。ワークフローは、i)印刷された後は隠され又は半ば隠されているパンタグラフ前景(14)及びパンタグラフ背景(16)、及び、ii)スキャン後は顕在化するパンタグラフ前景(14)の両方を有する前記複合ボイドパンタグラフ(12,TP)の少なくとも1つについて、進展される。 (もっと読む)

ボイドパンタグラフ及びボイドパンタグラフを生成する方法

ボイドパンタグラフ及びボイドパンタグラフを生成する方法が本明細書で示される。ボイドパンタグラフは所定のフィルタを使用して定義される画像の領域に基づく前景部分と、前記所定のフィルタを使用して定義される前記画像の他の領域に基づく背景部分とを有する。 (もっと読む)

41 - 50 / 155

[ Back to top ]